幕開け迫る「45nm時代」:この最新プロセスノードに設計者はどう備えるべきなのか?(3/3 ページ)

RDRは「あると便利」の位置付けか?

ここ数年間、ファウンドリはICの歩留りを向上させるために、設計チームに対してRDRの適用を強制しなければならなくなると言われてきた。その背景にあるのは、設計の規模、設計にかかわるルールファイルの数、リソグラフィにおける問題の数、マスクコストの増加である。ファウンドリの中には、近い将来、45nmノードでRDRを必須とすることを真剣に検討しているところもある。例えば、UMC社はここ2年間、45nmプロセスの開発に取り組んでいる。2006年第1四半期には最初の45nmテストプロセスについての発表を行い、2007年の第3四半期までには5件のテープアウトを行う予定としていた。また同社の45nm LL(low leakage)プロセスについては、2007年末までにパイロット生産の準備を整える予定である。UMC社のBamdad氏は、「プロセス開発を進める中で、次のことに気が付いた。それは、RDRの適用により、顧客は高い歩留りが得られる設計を行い、市場に対して迅速に製品を提供できるということだ」と語る。「例えば、ポリシリコンの配置方向が大きな問題になりつつある。詳細については検討中だが、顧客に対し、SRAMやスタンダードセルに対してポリシリコンを配置する向きを指定するかもしれない。このようなことが必須の規則となると考えている」(同氏)という。

IBM社は、SOIプロセスにおいてRDRの適用を必須としている。CPTAを通じて同社のプロセスアライアンスパートナとなっているChartered社のNg氏によると、「CPTAの顧客からは、現在、CPTAのバルクCMOSプロセスにもこれらの規則を適用してほしいとの要求が挙がっている」という。RDRを適切に利用することにより、最初から適切な設計が行える可能性が高まるからだ。それにより、設計上の繰り返し作業や手戻りが減り、さらにはもっと大きな問題であるマスクコストの増加も抑えられると期待する顧客が多いのだという。

Mentor社のDesign-to-Silicon部門担当バイスプレジデント兼ゼネラルマネジャであるJoe Sawicki氏は、「液浸リソグラフィを用いれば、本質的に65nmノードの乾式リソグラフィと同等の品質が得られる。そのため、45nmノードではRDRはまだ必要ないかもしれない」と述べる。「65nmでRDRなしで対応できたのであれば、45nmでもなしで対応できるだろう。RDRの適用を後押ししているのは、2D構造の『実現が困難』だという事実だ。しかし、45nmから32nm、22nmへと移行していくと、『実現が困難』という状態から、どのように実現すればよいのか『まったく見当もつかない』状態になる。22nmプロセスでは、そうした2D構造を1回のエッチングや1回のマスクプロセスで実現するのは不可能だ」と同氏は語る。その上で、「RDRは、ファウンドリが製造装置やフローを大幅に変更することなく、新しいプロセスノードを導入するのを支援する方法だ」と同氏は説明する。さらに「リソグラフィや製造におけるその他の技術の進歩により、32nmノードや22nmノードにおけるRDRの必要性は低くなるかもしれない」(同氏)とも指摘する。

Synopsys社のChilton氏は、「まだどの顧客からもRDRを利用しているとは聞いていない」と語る。「ルールベースの手法からモデルベースの手法への移行が考えられてはいるが、現時点では従来からの設計ルールに従っているようだ」と同氏は述べる。

RDRについては賛否両論があり、「設計フローの複雑さを緩和することができるのか」といった疑問の声が挙がっている。また、「市販の配線ツールは、ゲート数が増加するに連れ、ますます増大するDRCデッキに加えて、大量のDFMルール/モデルに対応しなければならなくなるのか」といった議論が巻き起こっている。ファウンドリ関係者らは、「65nmノード向けの一部の市販配線ツールでは、45nmノードの大規模な設計やより複雑なルール/モデルが原因となって、RDRを適用しないで実装フローに対応させることが難しくなっている」と指摘する。

EDAベンダーは、すでにこうした問題に対処しようとしている。Mentor社とCadence社は、45nmプロセスの複雑さに対応した新しい配線技術を開発したと主張している。Mentor社は、2007年6月に米Sierra Design Automation社を買収した。Sierra社の配線ツールを45nmの実装フローに対応させ、Mentor社のCalibre製品ラインを実装フローにさらに統合するべく、現在ファウンドリと共同で作業中である。またCadence社は2007年9月、同社のカスタム配線技術をEncounterプラットフォームに追加したことを発表している。Cadence社のデジタルIC実装担当バイスプレジデントであるEric Filseth氏は、「65nmノードでもそうだが、45nmノードでは、『普通の配線ツール』と『優れた配線ツール』の差がはっきりと現れる」と述べる。

SSTAに対する“温度差”

研究機関やEDAコミュニティは、将来のプロセスノードにおいて、SSTAツールなどの確率解析ツールが従来の静的解析ツールに取って代わるだろうと予測している。それに対し、ファウンドリは「65nmノードについて言えば、そのようなことは起きていない」としている。他方、早くから45nm技術に取り組んでいるEDAベンダーや、TSMC社、UMC社の関係者らは、「45nmノードからは確率解析が広く採用されるようになるかもしれない」と語っている。

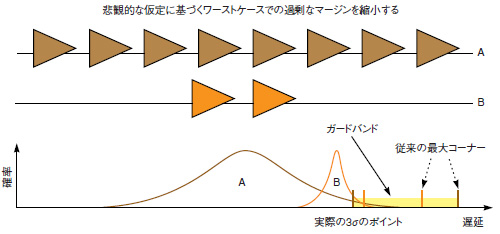

SSTAツールは、ワーストケースのタイミングモデル(従来からの配線負荷モデル)ではなく、統計的手法を用いたモデルを利用することで、より現実的かつ正確な回路動作の解析を実現する。これにより、過剰に大きいマージンを確保する必要がなくなる(図3)。例えば、各プロセスに対応したスタンダードセルライブラリの特性定義に統計的モデルを利用することで、設計者は小規模の回路、ブロック、あるいはチップ全体の動作を解析することが可能になる。回路のタイミングパラメータを導き、その結果を用いて性能を微調整するよう設計に変更を加えたり、消費電力を低減したりすることができる。

米Texas Instruments社のワールドワイドEDA戦略担当マネジャであるMike Fazeli氏や、同社のASICバックプレーン担当マネジャであるClive Bittlestone氏によると、「45nmノードでは、設計規模と複雑さが増大する。そのような状況下では、当社を含む一部の設計者にとって、SSTAツールが有用なものであることが立証されてきた」という。その事実とは裏腹に、ファウンドリはSSTAツールをタイミング検証におけるサインオフにすぐに利用しようとはしていない。また、市販のSSTAツールは使うのが難しいと感じる設計者もいる。Synopsys社のChilton氏は、「SSTAが扱うような事柄を、サインオフの条件に適用するのは難しい。従来のルールベースのサインオフから、よりソフトなものへと移行するのは、大きな変更となる。これは、技術的な問題というよりも、“文化”の問題だ」と述べる。

Chartered社のNg氏は、SSTAツールが45nmノードで広く使用されるようになるということについては懐疑的である。同氏は「SSTAツールが大きな可能性を秘めているということには誰もが同意するが、問題なのはどのような実装で実現されるかだ」と語る。それに対し、EDA企業や、TSMC社、UMC社らのファウンドリは、「確率解析ツールは成熟しつつある」と考えている。実際、米Extreme DA社、Magma社、Synopsys社らは、1年以上前からSSTAツールを提供している。Cadence社も2007年9月に「Encounter Timing System GXL」を発表した。TSMC社のQuan氏は、「米Altos Design Automation社の『Variety』のようなスタンダードセルライブラリ向けのSSTA性能評価ツールは、設計フローの確立に役立ってきた。ファウンドリや設計者が統計的解析ツールをより効果的に利用できるように、ライブラリの特性を定義することを支援してくれるからだ」と語る。

TSMC社はリファレンスフロー8.0においてAltos Design社のツールを認定し、顧客に対して45nmプロセスの統計的モデルを提供している。またリファレンスフロー8.0には統計的リーク解析も追加されおり、設計者はTSMC社の統計的モデルと解析手法をリークの問題に適用することができる。

なお、Magma社などのEDAベンダーは、このようなツールを提供し始めたばかりである。

IC設計者に求められる心構え

ファウンドリは、65nm/90nmノードにおける設計の課題に対処した経験を持つ設計者にとっては、45nmノードへの移行は比較的容易なことだと考えている。また、多くのIC設計者が、45nmノードに対してそれほど脅威を感じることなく、90nm、65nmを飛び越して、130nmから直接45nmへの移行を考慮してくれることを期待している。しかし、本稿で述べた通り、45nmノードでは従来とは異なり、低消費電力設計やDFMツールの利用が必須となる。さらには、RDRや確率解析ツールも必要になるかもしれない。

設計者にとって、45nmプロセスに取り組むには少なからず壁がある。ただし、その壁に立ち向かう前に認識しておくべきことは、プロセスが新しくなるたびに設計面で新たな課題が出現し続けるということである。45nmノードでは、本稿で述べたような新技術に対応することだけでなく、チップのアーキテクチャ開発、ソフトウエア開発、ロジック設計/検証においても、新たな、そして大きな課題が顕在化することになるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

図3 SSTAツールの概念 SSTAツールは、パフォーマンスの改善と電力の削減を実現する可能性を秘めている。技術自体は成熟しているが、45nmノードで広く採用されるか否かは現時点では不明である。

図3 SSTAツールの概念 SSTAツールは、パフォーマンスの改善と電力の削減を実現する可能性を秘めている。技術自体は成熟しているが、45nmノードで広く採用されるか否かは現時点では不明である。