DC-DCコンバータのノイズ対策[実践編]:徹底研究! 設計/実装における具体策(2/5 ページ)

■出力インダクタ下部

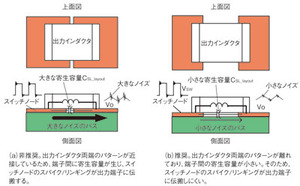

出力インダクタ下部のレイアウトでは、出力インダクタの電極間のパターンをなるべく離すことが重要である(図5)。なぜなら、電極パターンが出力インダクタの下まで張り出していると、同インダクタ両端の間に寄生容量が生じることになるからだ。そうすると、パワーMOSFETと出力インダクタの間のスイッチノードに発生する高周波のスパイク/リンギング電圧が、同インダクタ下の寄生容量を介して出力電圧にノイズとして現われてしまうのである。

例えば、寄生容量CSL_layoutの値が10pFだとすると、200MHzの周波数ではインピーダンスが80Ωとなる。そのため、出力インピーダンスによっては、スイッチノードのノイズがのってしまう。

■出力インダクタ/出力コンデンサ部

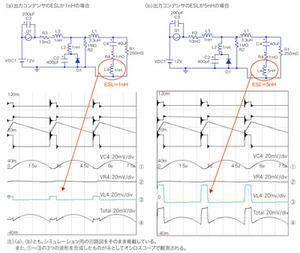

出力インダクタに流れる大きな電流はリップル電流(脈流)であり、Cin、Q1、Q2から成るリンギングループのように、高周波のスパイク/リンギング電流が流れることはない。ただし、出力コンデンサの寄生インダクタによって、出力のリップル波形が大きく変わるので注意が必要である。

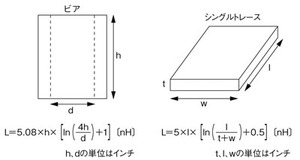

このことを表す例として、図6にシミュレーション結果を示した。この例では、出力コンデンサとしてセラミックコンデンサを使った場合を想定し、2つの条件でシミュレーションを行った。1つは、出力コンデンサのESLが1nHの場合である。もう1つは、コンデンサからグラウンドへのレイアウトが不適切で、5nHのESLが存在する場合のものだ。出力インダクタのリップル電流が仮に4A/μsであったとしたら、セラミックコンデンサのESLのみであればESL×di/dt=4mVになり、出力電圧のリップル波形にこの4mVの段差ができることになる(図6(a))。一方、ESL=5nHであるとすると、ESL×di/dt=20mVの段差ができる(図6(b))。わずか数nHの違いだが、出力電圧のリップル波形に大きな影響が及ぶことがわかる。数nHというのは、レイアウトパターンの長さにして数mm、あるいはビアの存在によって容易に形成されるレベルのインダクタンスである。図7に、パターンによる寄生インダクタンスの簡易的な計算方法を示しておくので参考にされたい。

なお、この例は本稿で主に扱っている数百MHzの高周波ノイズとして現われる現象ではない。しかし、わずか数nHのインダクタンスによって出力波形に大きな影響が及ぶことは確かなので、数mmという長さを意識してこの部分のレイアウトを行うことが重要である。

■電源コントローラIC

図1の3層目に示したように、電源コントローラICのアナロググラウンドは“静かなグラウンド”に接続する。大電流の流れる部品面のグラウンドではなく、内層のベタグラウンドで、出力側に近いところがよい。電源コントローラICのアナロググラウンドと出力グラウンドを島として囲むと、一点接地となって、より確実である。

■一点接地の考え方

一点接地という言葉は、パワーステージのグラウンドに使うケースと、パワーステージと電源コントローラICのアナロググラウンドとの接続に使うケースがあるので注意が必要である。

パワーステージに関しては「一点」というよりも、入力側の大電流パルス部のグラウンドと出力側のLCフィルタ部のグラウンドを島のイメージでまとめればよい。一方、パワーステージと電源コントローラICのアナロググラウンドとの接続における一点接地は、前項で説明したように、電源コントローラICのアナロググラウンドをパワーグラウンドの静かなところに接続する形となる。通常は、出力コンデンサのグラウンド付近に接続すればよい。ベタグラウンド層で島にすると確実だ。

Copyright © ITmedia, Inc. All Rights Reserved.