SiGeが切り開く半導体の未来(2/2 ページ)

SiGeがもたらすメリット

物理学と量子力学の理論上、HBTは何百ギガヘルツもの高速性を実現可能である。一方、シリコンのみの製造プロセスで速度を増加させるには、デバイスサイズの縮小という、HBTと比較して少し強引な手段をとることになる。最近の微細プロセスでは、この縮小による弊害として、トランジスタが破壊しないように、電源電圧を下げる必要があった。デジタル回路では、トランジスタはオン/オフの状態のみを伝達すればよい。そのため、この縮小という方法でもよいのだが、アナログ回路においては電源電圧を下げることでS/N比がすぐに限界に達してしまう。例えば、100GHzの動作周波数を達成するには、CMOSにおける縮小という手法を用いる場合、電源電圧を1V以下にしなければならない。

Maxim社のIC設計担当シニアサイエンティストであるJean-Marc Mourant氏は、「CMOSの本当の限界は、電源電圧を下げ続けなければならないことにある」と指摘する。その上で同氏は、「CMOSの製造プロセスは、コストと集積度が最重要課題である用途でしか使用できない」と付け加えた。

SiGe HBTにおいては、SiGeトランジスタのベースは、シリコンとエピタキシャル反応によって蒸着するゲルマニウムが結合する領域にある。この構造から、CMOSの製造プロセスにSiGeトランジスタの製造工程を加えるには、エピタキシャル反応装置を購入するだけで済み、そのほかのフローはそのままでよい。つまり、SiGe HBTの導入は、ほかの化合物半導体などと比較すると非常に容易である。

SiGeバイポーラにおけるシリコン格子内のゲルマニウムは、CMOSにおいて歪シリコンを実現するためのゲルマニウム注入チャンネルよりも、かなり多くの利点をもたらす。SiGe HBTでも歪シリコンの場合と同様に移動度が増すが、バンドギャップの変化による利点のほうが大きいのである。

例えば、ゲルマニウムを利用することにより、ベース領域におけるドーパント(不純物)の浸透性は高まる。TCAD(Technology Computer Aided Design)シミュレーションソフトウエアメーカーである米Silvaco社で製品ラインマネジャを務めるDerek Kimpton氏は、「SiGe HBTでは、電流増幅度を損ねることなく、ベース部の抵抗を下げられる。このことは、RF ICなどのように低ノイズであることが要求されるデバイスを製造する際に有利に働く」と指摘している。

また、ファブレスメーカーである米Inphi社で技術担当ディレクタを務めるRobb Johnson博士は、「ほかのすべてのHBTと同様に、SiGe HBTの背景にある概念は、ベースとエミッタの間に存在するバンドギャップによりベースのドーパント量を増加させることができるため、エミッタの注入効率が安定するということだ。つまり、デバイスの性能を犠牲にすることなくベースに対して一層のドープを進めることができ、それと同時にベースを薄くして高速性を得ることができる」と説明した。

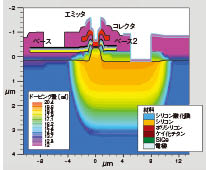

SiGeトランジスタでは、図4に示すように、ベースへのドーピングの濃度によって電子を加速する電界が生じる。従来のシリコントランジスタでは、ドーピング量が多いと電流増幅度が下がり、コレクタに逆戻りするリーク電流が生じてしまう。それに対し、SiGeトランジスタでは、バンドギャップの電位によって電流増幅度が最大化され、リーク電流が最小化される。ドーパント濃度が高いため、シリコンは絶縁体よりも金属に近い特性を示す。ベースの導電性は高まり、ベース部の抵抗は低下し、SiGeトランジスタのノイズ指数は純粋なシリコンデバイスよりも優れたものとなる。ただし、ほかのすべてのアナログプロセスと同様に、トレードオフも生じる。例えば、エミッタ部の抵抗を低くするか、それともリーク電流を抑えるのかといったことがトレードオフ要因となる。

このようにSiGeは、ほかのプロセスと少ししか変わらない製造ラインを用いて、上記のような大きな性能の改善を実現する。

Texas Instruments社のフェローであるMarco Corsi氏は、「普通のトランジスタでベースのドーパントを増加させると、ベース部の抵抗が低くなり、アーリー電圧を改善することができる。だが、そうすると、通常は電流増幅度が犠牲になる」と述べる。アーリー電圧(Early Voltage)の名前は、その発見者である米国のエンジニアJames M Early氏に由来している。アーリー効果(Early Effect)とは、印加されるベース‐コレクタ間電圧の変動に伴うBJT(Bipolar Junction Transistor:バイポーラ接合トランジスタ)のベース幅が変化する現象のことである。「電流増幅度が小さいと、高い電流密度でトランジスタを動作させることはできない。SiGeは電流増幅度を改善し、それによってベースのドーピング量を増やすことができる」とCorsi氏は述べる。

National Semiconductor社の主席技術者であるMike Maida氏は、「シリコンにゲルマニウムを加えることにより、バンドギャップを距離の関数として可変にすることができる。つまり、電流増幅度を調整するもう1つの手段が得られるのだ」と述べた。同氏によると、「電流増幅度と引き換えに、ベース部の抵抗が上がることはない」という。ベース部の抵抗により熱ノイズが生じ、ベース部の抵抗が高くなると最大周波数も低くなる。なお、Analog Devices社のフェローであるBrad Scharf氏は、「ゲルマニウムの添加と直接には関係のない、サイズの縮小などの要因によってもベース部の抵抗は低下する」と述べている。IBM社で派生技術/付加価値技術開発を担当するフェロー兼ディレクタのDavid Harame氏は、「こうした利点のすべてが、より良いトランジスタを製造することにつながる」と説明している。さらに、Texas Instruments社のCorsi氏は、「SiGeにより、全体的な性能指標を向上させることができる。特にpnp型のトランジスタで、npn型のトランジスタにかなり近い性能が得られることは特筆に値する。この対称性は、オペアンプや線形回路の設計に最適だ」と述べる。

SiGeは“万能”か?

ここまで、SiGeの製造プロセスを用いれば、良いこと尽くめであるかのように説明してきた。だが、SiGeプロセスに何の問題もないというわけではない。

ほとんどすべてのアナログ半導体企業が、ある工場から別の工場へとプロセスを移管した際、そのプロセスを利用できなくなったという深刻な事態を経験している。このことからわかるように、製造装置を用意するだけで、新たな製造プロセスを実現したり、歩留りを改善したりすることはできない。米Cypress Semiconductor社でプロセス技術開発エンジニアリングマネジャを務めるArtur Balasinski氏は、「製造プロセスのステップが増えるということは、歩留りが低下するということを意味する。ステップが10%増えれば、歩留りは自動的に数パーセント低くなる」と述べる。

SiGe BiCMOSは、コスト面で不利である。BiCMOSプロセスは、線幅が広く、トランジスタのサイズが大きいため、最新のCMOSプロセスを用いた場合よりもチップが大きくなる。BiCMOSのマスクセットは比較的安価だが、ほとんどがデジタル回路である製品を同プロセスで実現することには意味がない。「2世代前のレベルのプロセスに戻って、単に『より高速』であるだけのものを製造しても、競合他社に対して優位に立つことはできない。そのため、BiCMOSを使用しようという気にはならない」とCypress社のBalasinski氏は語る。

SiGeを選択すべきか否かは、各企業の状況、能力、戦略に大きく依存する。National Semiconductor社はインターフェースICの製造プロセスにSiGe BiCMOS採用している。例えば、5ギガビット/秒、10ギガビット/秒といった高速シリアルデータストリームに対応するには、シリアライザやデシリアライザを構成する部品として高速トランジスタが必要になる。このI/O部分は、アナログ回路である。従って、この戦略は非常に有効だと言えるだろう。チップ内部に信号を通せば、後はパラレルデータの処理であり、その速度は従来のCMOSで対処できるレベルである。こうした部品にはデジタル処理の要件がほとんどないため、BiCMOSプロセスによるチップサイズの大きさを考慮しても、SiGeを採用することのメリットは大きいのだ。

設計/製造上の問題

SiGeの利点として、既存のツールでデバイスモデルに対応できることが挙げられる。IBM社の主席技術者であるSubramanian S Iyer氏は、「アナログデバイスのモデルには、高い精度が必要となる。われわれは、これまで堅牢で正確なSiGeのモデルを提供してきたし、これからも提供し続ける。こうしたモデルの作成/検証に多大な労力をかけてきたため、アナログ/ミックスドシグナルIC製品でかなりの成功を収めることができた」と述べる。

しかし、同氏の見解のとおり、優れたモデルが開発できたからといって、何の問題もなく、SiGeバイポーラをCMOSの設計フローに追加することができるわけではない。Cypress社のBalasinski氏は、「多くの場合、CMOSの世界では、アナログについては別のデバイスモデルを使用する。これにBiCMOSの複雑なモデリングを加えると、考慮しなければならないことが爆発的に増えて、お手上げの状態になってしまうだろう」と指摘する。その上で同氏は、「数多くのモデルの開発、検証、校正、メンテナンスや、モデルの正当性を検証するためのラインの確保、モデルが実際のデバイス特性から逸脱していないことの確認に、かなりの労力が必要となる」と付け加える。

さらに、開発したデバイスモデルを製品化するとなると、より過酷な作業が生じる。例えば、開発したデバイスモデルを台湾TSMC(Taiwan Semiconductor Manufacturing Company)社の工場に対応させたいと考えたとしよう。その場合、「モデルを正確に複製することは可能だが、TSMC社はまったく異なるツールセットを使用しているかもしれないので、複製前後の結果を一致させるのは簡単な作業ではない」(Balasinski氏)という。さらにこの問題を複雑にするのは、すべてのアナログプロセスは、変化に対して非常に敏感であるということだ。「ほんの小さな事柄が、ある工場の製品は問題なく動作するのに、別の工場の製品には不具合があるという状況を引き起こすことがある」と同氏は語る。

これと同じことが、CMOSにおける歪シリコンについても当てはまる。米Freescale Semiconductor社で32nmバルク集積担当マネジャを務めるSri Samavedam氏は、「一般的に、SiGeプロセスは変化に対して敏感だ。製造プロセスを調整したり、何らかの変更を加えたりすると、すべてのパラメータを必ず再評価しなければならなくなる」と述べる。

Analog Devices社の設計エンジニアであるMarc Goldfarb氏は、「トレンチ分離と絶縁層分離もモデルに影響を及ぼす」と指摘する。「トレンチ分離と絶縁層分離による熱効果はわずかに異なる」(同氏)という。つまり、熱効果を考慮する必要があるのだ。

SiGeを使用するのは、高性能なICを設計する場合であることが多い。そのため、その部品が正しく動作することを確認するためには高度なツールが必要となる。とはいえ、SiGeのデバイスモデルには、米Cadence Design Systems社の「Orcad PSpice」やSynopsys社の「HSPICE」といった標準的なSPICEツールで対処することができる。

また、SiGeを利用したICは、RF周波数近くで動作することが多い。そのため、回路間に障害となるクロストークや相互作用がないことを確認するために、電磁界解析ツールも利用できるとよいだろう*4)。

デザインルールの確立を支援する物理モデリングが可能なツールセットもあるとよいかもしれない。Synopsys社のBorge氏は、「われわれは計算グリッド、つまりメッシュを使用している。そのグリッド上で、物理方程式に基づいた半導体の方程式を解く処理が行われる。また、最近では、pチャンネルMOSFETのチャンネルについて、量子力学の影響を考慮する必要が生じた」と説明する。まとめると、SiGeトランジスタをモデル化して解析するには、SPICEエンジンやRF用電磁界解析ツール、物理モデリングツールなどが必要となるということである。

競合技術との違い

SiGeの将来の見通しは、最大の競合であるGaAsや、インジウムリン(InP)などの?‐V族半導体の存在を考慮してもなお明るい。?‐V族半導体はSiGeよりもさらに高速だが、より高価でもある。また、?‐V族半導体には有効な酸化膜が存在しないため、チップ上にサブシステム全体を集積する場合には魅力的な選択肢とはならない。加えて、これらのICを製造可能な工場は、一般的には6インチ(約15cm)までのウェーハしか扱えない。さらに、製造プロセスに特殊な要件があるため、CMOSプロセスを改変する程度では対応することができない。

特にRFの分野では、SiGeのメリットが大きな訴求力を持つ。National Semiconductor社のMaida氏は、「SiGeのRFパワーアンプには大きな利点がある。しかも、それをCMOSベースのチップに集積することができる。高価で難解なGaAsに比べると、そのメリットは大きい」とSiGeプロセスの有用性を強調した。

脚注

※4…『電磁界解析ツール活用のススメ』(Paul Rako、EDN Japan 2007年4月号、p.51)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング