新規格USB3.0、計測面ではどう変わった?:高速シリアル・インターフェイス入門(5)(2/4 ページ)

USB3.0の高速化を支える技術

ここからは、本連載の第1回で示した高速伝送を支える技術のキーワードに従って解説をしていくことにしますが、同時に、信号計測における技術的課題と対策についても説明していきたいと思います。

LVDS

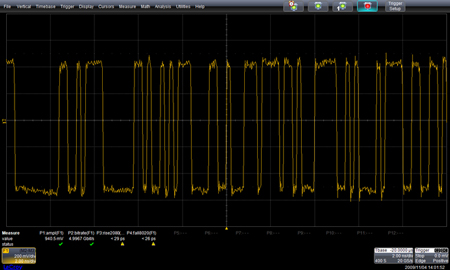

「なぜいま、高速シリアル・インターフェイスなのか?」で解説したように、高速化に有効な手法として低振幅を挙げましたが、USB3.0では、PCI Expressと同様に差動信号の振幅で最低0.8V、最高1.2Vと規定されています。図2にはUSB3.0の信号を示しています。振幅は、0.94V、デエンファシスは掛けられておらず、理想的な信号となっています。

CRU(Clock Recovery Unit)

USB3.0は前回のPCI Expressと同様に、クロックはデータ信号に埋め込まれているエンベッデド・クロックという方式を使っています。規格内で規定されるJTF(Jitter Transfer Function)は、PCI Expressなどと同じく、送信器信号評価用に規定されたものです。

帯域が10MHzの2次特性であり、ダンピング係数0.707、ピーキングは最大2dBになると規定されています。こうしたジッタ計測のより詳しい内容については、2009年1月15日付で出されているUSB 3.0 CDR Model White Paper Revision 0.5に掲載されています。

伝送線路とISI

USB3.0では、利便性の意味合いからUSB2.0との下位互換性を重視しています。移行が容易なように、従来のUSB2.0で利用されてきた設計環境をなるべく変更しないことを目指しています。マザーボード上でのチップの配置、コネクタの設置位置と配線方法などです。

また、ホスト側で2種類、デバイス側で1種類の合計3つのモデルが実装条件として考慮されています。ホストでは、フロントパネルにコネクタを設置する場合は、基板上のトレースは3.5インチと比較的短いのですが、そこから8インチのケーブルを使って接続するとモデル化されています。リアパネルにコネクタを設置する場合には、逆に基板上を12インチの長いトレースを引き回し、コネクタは基板上に直接取り付けるとモデル化されています。

デバイスに関しては、コネクタから非常に短いトレースでチップに接続されているとモデル化されています。このホストとデバイスの間を、3mのUSB3.0ケーブルで接続した状態で十分に低いエラーレートで通信ができるように、信号品質を確保しなければなりません。

USB3.0では、こうした実装方法をモデル化したReference Channel基板を作り、モデル化した実装方法におけるISIを規定できるようにしています。このReference Channel基板は、USB-IFが供給する計画になっていますが、Sパラメータの形でも供給されるのでエミュレーションを使って代用することが可能になっています。

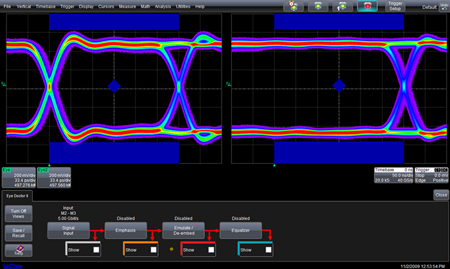

図3には、USB3.0のトランスミッタの出力から直接捕捉した信号波形を示します。

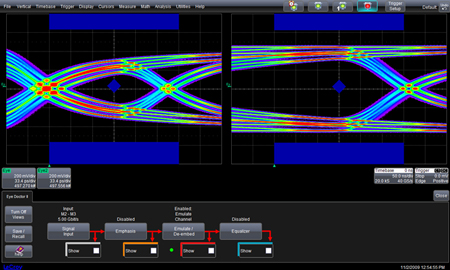

この信号波形に対しReference ChannelのSパラメータを適用してチャンネルのエミュレーションを行った波形を、図4に示しました。図4では、Reference Channelの損失により大きなISIが生じており、レベルが複数本に別れ、クロスポイントも大きく4点に分かれてしまっていることが分かります。

デエンファシス

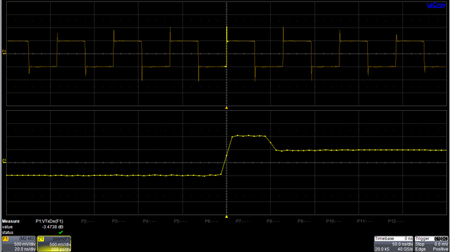

このように、USB3.0では実装上大きなISIが発生することが想定されているため、PCI Express同様に、デエンファシスの技術が採用されています。しかしながら、PCI ExpressのGen2であったような6dBの設定はなく、3.5dBのみの設定になっています。

図5には、デエンファシスが掛かった信号を示します。デエンファシスの比率を計測するには、この図のように周期の長いパターン(CP7)を使って計測するように想定されています。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 USB3.0の信号

図2 USB3.0の信号 図3 USB3.0のトランスミッタの出力波形

図3 USB3.0のトランスミッタの出力波形 図4 USB3.0のトランスミッタのエミュレーション波形

図4 USB3.0のトランスミッタのエミュレーション波形 図5 USB3.0のデエンファシス

図5 USB3.0のデエンファシス