ビット誤り率テスターを簡単に作る:Design Ideas 計測とテスト

デジタル通信において基本となる測定器、ビット誤り率テスターを、安価に製作するアイデアを紹介する。

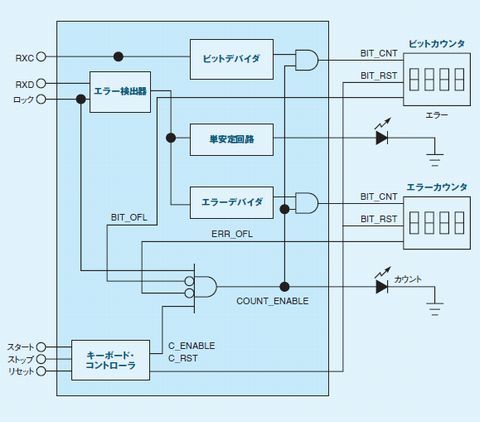

ビット誤り率(bit error rate:BER)テスターはデジタル通信において基本となる測定器である。多くの市販BERテスターが入手可能であるが、それらの代わりに安価なものを設計/製作することも容易だ。図1に示す回路は市販のBERテスター並の性能を有するが、表示されたデータに基づいて手計算で結果を出す必要がある。このテスターは受信ビット数と受信したエラービット数しか表示しないため、BERを求めるには電卓などを用いて、表示されたデータから算出しなければならない。

図1のテスターは、FPGAやCPLDのような、プログラマブル・ロジックICを1個と、2個のカウンタ・モジュールを用いて作ることができる。カウンタ・モジュールは、液晶またはLEDを使用したもので、4桁以上を表示でき、オーバーフロー表示機能が付いている市販品を用いる。また、データクロック周期の半分ほどの狭いパルス幅の信号にも対応できなければならない。

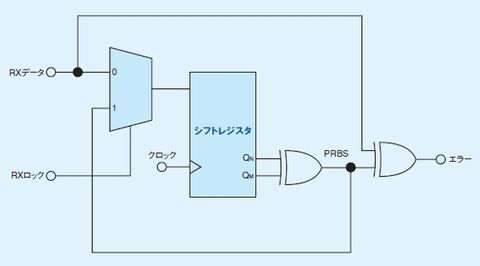

図2にエラー検出器の主要部分を示す。この検出器は、送信機と同じ擬似乱数ビット・シーケンス(PRBS)発生器を用いているが、1つの仕掛けが加えられている。測定中の復調器がロックされていないときには、シフトレジスタは受信データをロードし、エラービットの計数は行わない。各復調器は特別なバースト・モード復調器を除き、どの復調器でもBERはシステムが「ロックされた」ことを明示する前にある公称レートまで減少する。このようにして、シフトレジスタは高い確率で入力シーケンスに自己同期される。

復調器がロックされると、ロック信号がマルチプレクサの出力を切り替えてローカルにデータを発生する。このデータは、伝送されてきたデータのはずである。ローカル発生データがシフトレジスタに入力され、同時に測定が行われる。受信データとローカル発生データの間に相違があれば、それがビットエラーとなる。カウンタがパルスをカウントしている限り、エラー信号はRZフォーマットのクロックと一体になったものでなければならない。このようにするとテスターが2つの連続したエラーを1つのエラーとカウントしない。

復調器がロックされる直前にエラーが発生すると、シフトレジスタの初期設定が狂ってしまい、ローカル・シーケンスと受信シーケンスの相関が大幅にずれる。その結果、この場合のBERは0.5近くになる。この誤った状態は容易に検出でき、測定を再スタートすることができる。

図1に示すアーキテクチャでは、エラービット数とビット数を、エラーデバイダおよびビットデバイダ・ブロックで分割することができる。エラー数は1、10、100、1000で割ることができ、ビット数は104、105、106、および107で割ることができる。この分割機能によりテスターは、テスターがエラーカウント数を分割して低い値にしなければならないような低品質の信号を測定でき、さらにビット数の分割あるいは長い測定周期が必要となるような状況にわたるBER範囲も測定可能となる。

各ブロックは、2個のスイッチによって、簡単に分割数を決めることができる。間違いを避けるために、分割制御では、ディスプレイ上の小数点も制御するようにしたほうがよい。また、ディスプレイの下部に指示ラベルを付けて、実際の構成のための増倍率を示すようにするとよい。

もう1つの特徴はオーバーフローに関するものである。いずれかのカウンタ・ブロックがオーバーフローすると、図1の回路は、BIT_OFLおよびERR_OFLフラッグにより、ただちにエラーカウントを停止する。この機能は無人測定や、長い周期の測定を行っているときに、テスターが間違ったデータを表示しないようにするためのものである。BIT_OFLおよびERR_OFLフラッグがアクティブになると、COUNT_ENABLE信号をターンオフする。

スタート、ストップ、およびリセットキーはこの装置を制御するためのものである。これらは有限ステートマシンを駆動し、それによって、変数C_ENABLEおよびC_RESETを生成する。C_ENABLEはビットおよびエラーのカウントを制御し、C_RESETはカウンタのリセットを制御する。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 簡易BERテスターの回路図

図1 簡易BERテスターの回路図 図2 エラー検出回路

図2 エラー検出回路