高速シリアルの多レーン化がもたらすシグナルインテグリティの新たな課題:実装技術 シグナルインテグリティ(1/3 ページ)

電子設計の世界では、マルチレーン高速バスの採用が一般化し、設計の複雑化と高速化が進行中だ。それによって、シグナルインテグリティに関わる新たな問題が生じている。そこで米国のEDN誌は、シグナルインテグリティの専門家を取材し、彼らの見解を仮想的なパネルディスカッションとして誌上に再構成した。なお、シグナルインテグリティには数多くの要因があるが、本稿ではクロストークとEMIに焦点を絞っている。

高速ボード設計者が注力する課題とは?

マルチレーンの高速バスはシグナルインテグリティにどのような影響を与えるのか。それから生じる問題をいかに回避すればよいのか――。高速信号を扱うプリント基板の設計に取り組むベテランエンジニアたちは今、これらの課題に注力している。

Tektronixでシニアテクニカルマーケティングマネジャーを務めるChris Loberg氏とAsset InterTechの設計検証/テスト担当バイスプレジデントであるTim Caffee氏はともに、現在の高速プリント基板設計において高速バスにおける動作マージンが減少しており、それが課題を難しくする要因だという見解を示す。

TektronixのLoberg氏は、次のように指摘する。「高速基板の設計は今、データ伝送速度が10Gビット/秒を上回る高速シリアルインタフェースに向かっている。それにも関わらず、EMI(放射電磁雑音)やクロストークの要因になる信号パスの特性を改善できるような、コスト効率の高い、斬新なアーキテクチャはまだ見い出されていない。そのため、EMIやクロストークを最小化し、高速信号の受信側がシリアルバスの論理遷移を正確に判定できるようにするには、イコライゼーションなどの適応型の信号伝送技術を適用する必要がある」。

さらに同氏によれば、高速データ信号の周期(デジタル信号が“1”または“0”の状態を維持する期間)が短くなってきており、その結果、アイパターンを用いて信号の論理レベルの遷移やEMIあるいはクロストークを評価するという旧来から使われてきた手法が適用しにくくなっているという。アイパターンのクロスポイントやタイミングインテグリティを計測することがこれまで以上に難しくなってきたため、シグナルインテグリティを効率的に評価できなくなっている。

Asset InterTechのCaffee氏によると、高速バスが幾つも接続されると、信号周波数の上昇とともに動作マージンは次第に縮小し、ジッタやシンボル間干渉(Intersymbol Interference:ISI)、クロストークのような現象が発生し、高速SERDES(シリアライザ/デシリアライザ)やメモリチャネルのシグナルインテグリティが著しく悪化する。高速化および高周波化が一段回進むたびに、バスは歪みや異常状態の影響を受けやすくなってしまう。その結果、データの伝送が簡単に途絶えたり、システムの出力が停止してしまう危険性すらある。

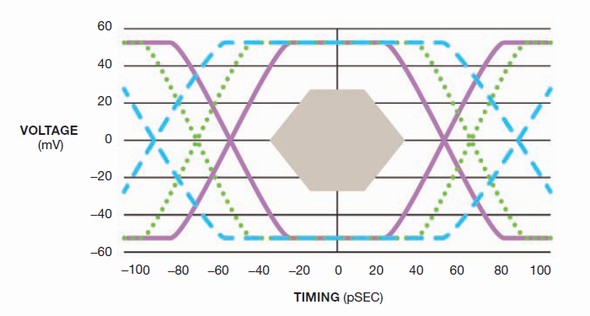

この問題を例示したのが図1のアイパターンだ。高速バスインタフェース規格の3世代にわたる変化を仮定し、信号周波数の上昇による影響と、その結果としてバスの動作マージンがどのように減少してしまうかを図示している。周波数が高まると、わずかな歪みでもデータ伝送の断絶が起こり得る。

図1 標準規格の世代が6Gビット/秒(青色の破線)から8Gビット/秒(緑色の点線)へ、さらに10Gビット/秒(紫色の実線)へと進むと、アイパターンは次第に小さくなり、この図の中心にあるスイートスポット(最良動作条件)近くまで閉じてしまう。出典:Asset InterTech

図1 標準規格の世代が6Gビット/秒(青色の破線)から8Gビット/秒(緑色の点線)へ、さらに10Gビット/秒(紫色の実線)へと進むと、アイパターンは次第に小さくなり、この図の中心にあるスイートスポット(最良動作条件)近くまで閉じてしまう。出典:Asset InterTechTeledyne LeCroyでシグナルインテグリティ関連製品のプロダクトマネジャーを務めるAlan Blankman氏は、25Gビット/秒を超えるような高ビットレートに加えて、PCI Express(PCIe)や40/100GBASE-R、Infinibandのように、複数レーンを用いる高速シリアルインタフェース(いわば“パラレル化シリアル”)の標準規格がシグナルインテグリティの問題を難しくしていると指摘する。「ビットレートが高くなれば、デジタルデータの伝送波形におけるエッジ(立ち上がり/立ち下り)部の高速化が必要になる。そうしたエッジ部の波形には、従来よりも高い周波数成分が含まれるので、コネクタやビア、パッケージなどを信号が通過する際にインピーダンスの不整合に起因した反射が大きくなってしまう。さらに、信号の損失が増大する上、近接する配線とのカップリングが大きくなってクロストークとEMIが増大する」(同氏)。

Agilent Technologiesでシグナルインテグリティ・プログラムのマネジャーを務めるShamree Howard氏は、「データ伝送が高速化すると、データを正確に捕捉するために、精度がより高いトリガーを使う必要があり、それが課題になる」と付け加える。同氏は、ジッタ測定が高速デジタルリンクの特性を評価する上での鍵になると述べ、さらに、次のようにコメントした。「ジッタの測定は、たとえボタン1つで実行できるような機能が測定器に備わっていたとしても、難しい課題であることに変わりはない。クロックリカバリや位相同期ループ(PLL)に関する情報に加えて、ジッタ成分解析、クロストークとその影響、複数の手法による波形統計なども考慮する必要があるからだ」。

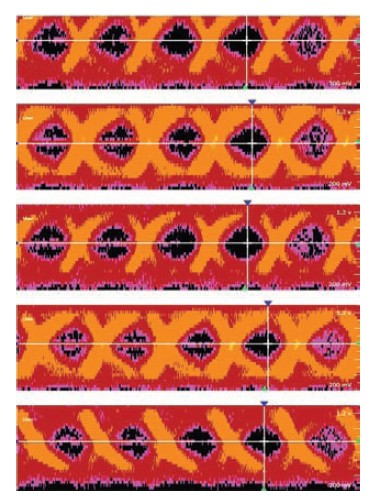

図2 Agilentのロジックアナライザ「U4154A」は、時間軸と電圧軸の両方でアイパターンの内側にあるポイントにサンプリング位置を自動的に設定し、アイパターンを捉える機能を備えている。時間軸の幅が100psで電圧軸の幅が100mVという小さなアイ開口部も観測することが可能だ。出典:Agilent Technologies

図2 Agilentのロジックアナライザ「U4154A」は、時間軸と電圧軸の両方でアイパターンの内側にあるポイントにサンプリング位置を自動的に設定し、アイパターンを捉える機能を備えている。時間軸の幅が100psで電圧軸の幅が100mVという小さなアイ開口部も観測することが可能だ。出典:Agilent Technologiesまた同氏は、Agilentが供給するAXIeベースの4Gビット/秒対応ロジックアナライザモジュール「U4154A」を使用すれば、時間軸方向が100psで電圧軸報告が100mVといった小さいアイ開口部を高い信頼性で測定できると述べている(図2)。

シグナルインテグリティの専門家でコンサルティング企業Signal Consultingを運営するHoward Johnson氏も、高速の回路では信号の観測それ自体が非常に難しくなることを強調する。「たとえその高速信号に対応可能なプローブが存在したとしても、回路中の観測したいポイントにそのプローブを配置できない場合もある」(同氏)。そこで同氏が提案するのが協調シミュレーションだ。すなわち、物理的な回路の開発に併せて、その回路のソフトウェアシミュレーションも同時に進めるという手法である。

やはりシグナルインテグリティのコンサルティングを手掛けるRansom’s NotesのRansom Stephens氏は、「オシロスコープの主要メーカーは新たな機種を投入しているが、クロストークを明確に自動検出するための手 法が確立されていないことが問題点だ」とみる。最新のテスト装置には、クロストークがビット誤り率(BER)に与える影響を推定できる機能が備わっているが、そうした機能はいずれも消去法によるものだ。

「クロストークを回避するのは理論的には単純だが、実際には不可能なことが多い」とStephens氏は話す。クロストークは、妨害源となる信号の論理レベルが遷移するときに発生するもので、立ち上がり/立ち下がりの時間を長くすれば(信号遷移を緩やかにすれば)、クロストークを減少させられる。また、クロストークは干渉による現象なので、信号の配線間隔を広げれば大きな抑制効果がある。

Stephens氏は、「差動構成を慎重に設計することが最良の方策と思われる。差動スキューを十分に小さくし、2つのトレースが上下になるべく重なるように配置できれば、差動信号伝送によるキャンセル効果が期待できる」としている。

Copyright © ITmedia, Inc. All Rights Reserved.