高速シリアルの多レーン化がもたらすシグナルインテグリティの新たな課題:実装技術 シグナルインテグリティ(3/3 ページ)

理想のツールを追い求める

測定器メーカーは、ジッタを解析したり、シグナルインテグリティを分析したりするツールを改善し続けているが、シグナルインテグリティに対する理想的なツールが利用できるようになるにはまだ時間がかかりそうだ。Signal ConsultingのJohnson氏は「次のトレンドとしては、電源網の特性を解析し、その電源網に対して特性を評価するための特殊な電流波形を注入できるような、装置と試験ソフトウェアをまとめたソリューションが登場するだろう」と予測する。Ransom’s NotesのStephens氏は、クロストークをより高度にイコライゼーションできる技術に期待しているという。

それでは既に今、市場に供給されているツールとしてはどのような製品が利用できるのだろうか。

オシロスコープ

シグナルインテグリティの分野では広帯域オシロスコープの真価が問われる。Teledyne LeCroyのBlankman氏は、NRZ(Non Return-to-Zero)シリアルデータパターンの立ち上がり時間が30psを下回る場合があると指摘する。同氏によれば、第3世代PCI Expressシステムのレシーバを試験するには帯域が13GHzのオシロスコープが求められ、トランスミッタの試験では20GHzのオシロスコープが必要になるという。

「Infinibandや40/100GBASE-Rなど、最近登場しつつあるマルチレーン方式は、チャネル数と帯域に対してこれまで以上に厳しい条件を突き付けるだろう」とBlankman氏は話す。同氏は、「これらの規格では、データ伝送速度が25Gビット/秒および28Gビット/秒に達する。その伝送波形を評価するには通常、基本周波数の4〜5倍に相当する50〜65GHzのオシロスコープが必要になる。Infinibandと40/100GBASE-Rはマルチレーン方式なので、シグナルインテグリティの問題を十分に解析するには8チャネルもしくは12チャネル、あるいはもっと多くのチャネルを同時に使用しなければならない」と述べ、続けてTeledyne LeCroyのハイエンドオシロスコープ「LabMaster 10 Zi」に言及した。このオシロスコープは、65GHzを超える帯域幅と、80ものチャネルを同期させて単一の装置として動作させられるチャネル同期アーキテクチャに特長があるという。

ネットワークアナライザ

ネットワークアナライザは、マルチレーンシステムでのクロストークを解析したり、試験対象デバイスの周波数特性を把握したりする際に重要な装置だ。アンリツの後藤氏は、Sパラメータ試験で最良のデータを得るには、広い周波数範囲をカバーするベクトルネットワークアナライザ(VNA)が必要だと指摘する。そうしたVNAとして同氏は、70k〜125GHzをカバーする同社の「VectorStar」シリーズを推奨する。

同氏は、「高域側の周波数成分は大きな減衰を受けるので、シグナルインテグリティの評価では測定範囲の下限周波数まで正確に測定することが重要だ。多くの場合、DC(直流)に可能な限り近い周波数まで測定することによって、モデルの精度を改善でき、高精度のアイパターンを生成することが可能になる」と述べている。

LeCroyのBlankman氏は、多ポートのネットワークアナライザは価格が非常に高いと指摘した。その上で同氏は、「LeCroyがシグナルインテグリティの測定に向けて開発したネットワークアナライザ『SPARQシリーズ』は、他社が供給する従来のVNAに比べて低価格の選択肢になる」と主張する(図4)。なおSPARQは、“S-parameters quick(Sパラメータを素早く)”という意味だという。

ソフトウェアツール

データ伝送速度が高まると、設計時により多くのシミュレーションが必要になるので、測定器メーカーは自社の装置と連携するソフトウェアツールの開発に注力している。TektronixのLoberg氏は、同社のオシロスコープの上で稼働するシリアルデータリンク分析(Serial Data Link Analysis:SDLA)ツールの有用性を訴求する(図5)。SDLAツールを使えば、イコライゼーションの効果をCadence Design SystemsやMentor Graphicsが提供するEDAツール環境でシミュレーションすることが可能だ。同氏によると、「そうして作成したソフトウェアモデルはオシロスコープに読み込むことができ、そのモデル特性をSパラメータに変換できる。そうして、イコライゼーションの効果をオシロスコープのフィルタに実装することが可能だ」という。これによりオシロスコープ上で測定対象の信号に実際にイコライザをかけて、アイの開口部を広げられるかどうかを観測できる。

Teledyne LeCroyもオシロスコープベースのシリアルデータ分析ソフトウェア「SDAIII-CompleteLinQ」を提供している。同社のBlankman氏は、「アイパターンとジッタ、垂直(電圧)ノイズを解析できるオシロスコープベースのソフトウェアを活用することが重要だ」と指摘する。また、同氏は、治具や接続部の影響を取り除いたり模擬的に生成したりでき、さらに、信号のトランスミッタやレシーバにイコライゼーション効果を適用できるツールキットが必要だと述べた。「ジッタやノイズの根源的な原因を把握するには、ジッタとノイズの変動や分布を周波数軸と時間軸で多面的にプロットできる解析用ツールキットが不可欠である」(同氏)。

ビット誤り率テスト装置

AgilentのHoward氏は、「現在ではほとんどの標準規格でレシーバの試験が義務付けられるようになっている。それにもかかわらず、設計者の多くは何から手を付けてよいのか分かっていないのが実情だ」と指摘する。さらに同氏は、「測定の精度を確保する上では、システムのキャリブレーションが重要だが、それは試験の中で最も難しい作業である」と付け加える。

同氏は、第3世代のPCI Expressでストレス信号を適切にキャリブレーションすることが簡単な作業ではないとの認識を示す。同氏は、レシーバのコンプライアンス試験用として、Agilentの高性能シリアルBERT(ビット誤り率テスト装置)「J-BERT N4903B」を推奨する。この装置は、レシーバのジッタ耐力を評価でき、PCI ExpresseやSATA/SAS、DisplayPort、USBといった現在広く普及している各種のシリアルバス規格との適合性を検証するために開発されたものだ。

アンリツの後藤氏は、BERTを選択する際には、固有ジッタの最も小さい機種を選ぶのが望ましいと指摘する。例えば、同社の「MP1800A」は、固有クロックジッタが350fs(rma値)以下である。このBERTは、正弦波ジッタやランダムジッタ、バウンデットアンコリレート・ジッタといった各種のジッタ成分を発生させるとともに、最大32.1Gビット/秒のスペクトラム拡散クロックを生成し、それらに対するジッタ耐力を高い再現性で安定に測定できるという。

組み込み型テスト装置

高速バスインタフェースの評価では、テストに物理的なプローブを使う時代は終わりつつある。物理的なプロービングそれ自体が、評価対象の信号に障害をもたらす可能性があるからだ。

それでは、今後はどのような手法が使われるのだろうか。組み込み型のテスト装置に対する関心が高まっており、テスト容易化設計(Design for Test:DFT)のコンセプトに基づいて、レシーバが受け取る信号データを非侵襲で取り出す手法が提案されている。Asset InterTechのCaffee氏は、「言い換えれば、シグナルインテグリティに取り組むエンジニアが求めるハードウェアデータに、ソフトウェアでアクセスできるようにする手法だ」と表現する。

組み込み型のテスト装置は、既に半導体チップの分野では長年にわたって、特性評価や検証、試験に使われてきた実績がある。そして現在では、レシーバが受信するデータを組み込み型テスト装置でモニタし、それを外部にリポートするという応用が進んでいる。Caffee氏によれば、外部から組み込み型テスト装置にアクセスする手段としては、例えばIEEE1149.1規格のバウンダリスキャン(JTAG)テストアクセスポートのように、標準的な技術が使えるという。

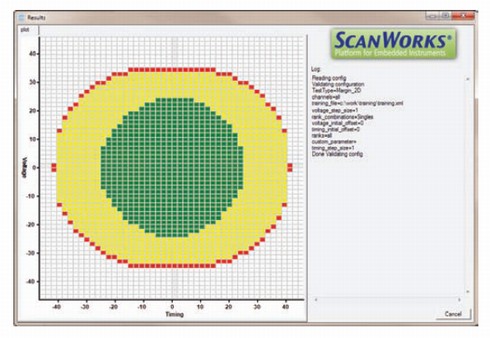

同氏は、「JTAGを介して、ソフトウェアベースの外部プラットフォームから埋め込み型テスト装置にアクセスできる。その外部プラットフォームは、埋め込み型テスト装置を管理するとともに、その装置が収集する測定データをコンパイル(翻訳)したり解析したりする役割を担うものだ」と説明した(図6)。

関連キーワード

計測機器 | オシロスコープ | アジレント・テクノロジー | EMI(電磁妨害) | アンリツ | 高速バス | ネットワークアナライザ | テクトロニクス | インタフェース | PCI Express | 100ギガビットイーサネット | ロジックアナライザ | プリント基板 | コンプライアンス | 実装技術(エレクトロニクス) | メンター・グラフィックス | PLL | Serial ATA

Copyright © ITmedia, Inc. All Rights Reserved.