完全統合型の信号/電源アイソレーターを用いた低放射の実現:信号と電源の絶縁をワンチップで(2/4 ページ)

手順1:適切な統合型デバイスの選定

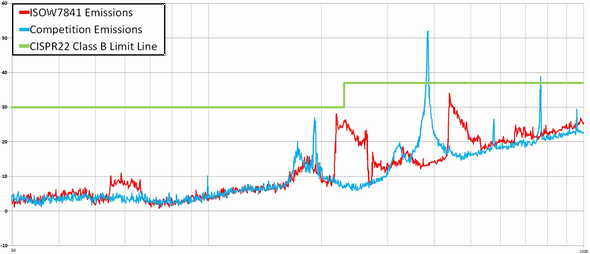

既存の統合型の信号/電源絶縁ソリューションは、電磁気放射の点から全てが同じではありません。慎重に回路設計とクロック管理を行えば、デバイスレベルで電磁気放射を小さくできます。図4に、CISPR(国際無線障害特別委員会)22Bの放射要件をシンプルな評価ボードによって満たすデバイスの例と、満たさないデバイスの例を示しています。この比較をチップレベルで行い、放射が少ないデバイスを選定することが重要です。

手順2:低い入力電圧での動作

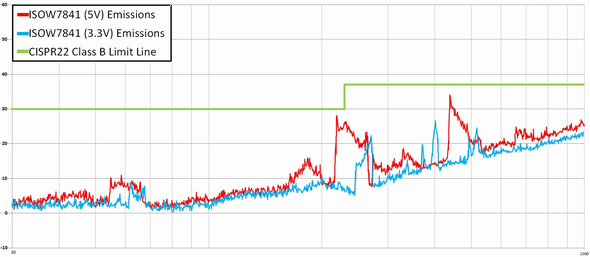

絶縁型パワーデバイスは、標準電源である3.3Vと5V両方との互換性のため、広い入力電圧範囲(通常3〜5.5V)に対応します。5Vと比較して、3.3V動作時は、パワートランジスタの低電圧駆動により、内部DC-DCコンバーターのスルーレートは低くなります。この結果、絶縁バリアをまたぐコモンモード電流は減少し、放射も小さくなります。図5から分かるように、3.3V電源での放射は5V電源の場合より大幅に小さくなります。

手順3:入出力デカップリングコンデンサー、入力バラスト抵抗、フェライトビーズ

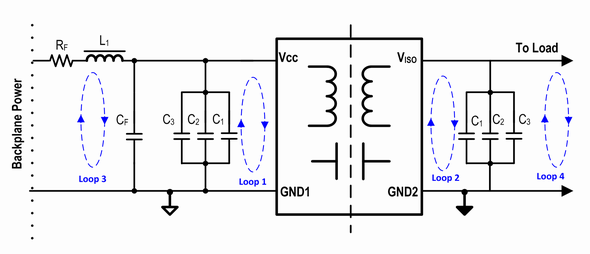

先ほど述べたように、完全統合型の絶縁型電源を持つデバイスは、トランスの低いインダクタンスを補うため高速のスイッチング周波数を使用します。このようなデバイスでは、レギュレーションを維持しながら、要求された出力DC負荷を供給するために、何らかの形で電力変換のデューティサイクル制御を行います。コンバーターがオンになると、入力電源電圧VCCから大きな電流が流れます(図6)。この電流には、低周波成分(レギュレーションの閉ループ帯域幅にほぼ比例)と高周波成分(DC-DCコンバーターのスイッチング周波数とその高調波)が含まれます。

集積回路(IC)入力部のさまざまな容量の入力コンデンサーバンク(C1=100nF、C2=1μF、C3=100nF)は、高周波成分の多くを取り除き、バックプレーンの電源経路への伝播(でんぱ)を阻止します。ループ1の面積を抑えるため、これらのコンデンサーはICのできるだけ近くに配置することが重要です。容量が最小のコンデンサーをICの一番近くに取り付けます。出力側に配置される同様のコンデンサーバンクは、DC-DCコンバーター2次側のスイッチング電流を除去します。ループ2の面積を最小にすることが重要です。

デカップリングコンデンサーがあっても、バックプレーン電源経路には電源ネットワークの出力インピーダンスによっては高周波と低周波の電流が流れる(ピーク電流100〜500mAで数マイクロ秒継続)ことがあります。入力電源経路が長い場合は、バラスティング抵抗(RS)および追加の大容量コンデンサー(CF)によって、入力電源経路への電流の流入を阻止し、放射を小さくできます。これは、ループ3内の電流減少に有効です。

RSの推奨値は、VISOで全負荷時(130mA)の1Ωから軽負荷時(10mA未満)の5Ωです。CFの推奨値は100μFです。放射結果に基づいて、これらの値を調整したり、重要でない部品を除去したりできます。フェライトビーズ(L1)を設計に含めれば、高周波ノイズのバックプレーン到達を防止できます。

図7は、レイアウト例のイメージで、デカップリングコンデンサーの配置を示しています。このレイアウトでは、全グランドプレーンを接続する基板エッジ沿いのスティッチングビアによってファラデーシールドが形成されます。これにより、ノイズが多い内部トレースやプレーンからの放射を阻止します。

Copyright © ITmedia, Inc. All Rights Reserved.

図4:「ISOW7841」と競合デバイスの放射(5V入力、80mA負荷時)

図4:「ISOW7841」と競合デバイスの放射(5V入力、80mA負荷時) 図5:「ISOW7841」の放射(5Vおよび3.3V入力時)

図5:「ISOW7841」の放射(5Vおよび3.3V入力時) 図6:電源のデカップリングコンデンサーと入力バラスティング抵抗

図6:電源のデカップリングコンデンサーと入力バラスティング抵抗 図7:「ISOW7841」評価モジュール

図7:「ISOW7841」評価モジュール