コンバーターの回路方式:DC-DCコンバーター活用講座(4) 電力安定化(4)(1/3 ページ)

今回の記事では、同期式と非同期式の違いの他、2段式やマルチフェーズといったコンバーターの回路方式について説明する。

同期式および非同期式変換

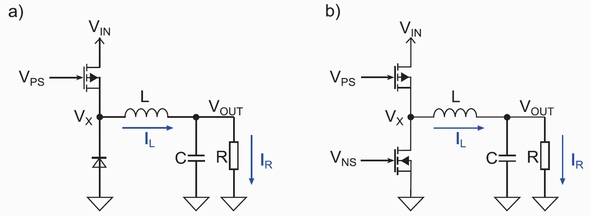

前回の記事で示したトポロジーでは、全てのデザインでキャッチ整流器としてダイオードが使われています。代わりの方法として、ダイオードをFETと置き換えることができます。FETはPWM信号に対して逆位相になる信号によってオンし、ダイオードの機能を代行します。FETとダイオードを使用している回路は非同期式と呼ばれ、2個のFETを使用している回路は同期式と呼ばれます。降圧コンバーターの2つの回路方式を図1に示します。

キャッチダイオードをFETと置き換えるといくつかの利点があります。FETのオン抵抗(RDS(on))は非常に低く、ダイオードと異なりその両端に順方向の電圧降下がないので、同期式デザインは高入力電流と低出力電圧の両方で効率が高くなります。効率は最大負荷条件で非常に大きく向上する場合があります。一般的な中位の電力の15W同期式コンバーターでは、非同期式のデザインに比べて、キャッチダイオードの消費する電力が4分の1にまで減少することがあるからです。もう1つの利点として、高電流FETはパワーダイオードより一般に小さいので、PCB上の占有面積を節約することができます。

非同期式回路に対する同期式回路の短所は、追加のFETとその駆動回路だけでなく、両方のFETが同時にオンするのを阻止するデッドタイムタイミング回路のための部品コストが増加します。もう1つの短所として、非常に小さい負荷では(最大負荷の10%未満)、同期式デザインは非同期式デザインより実際には効率が低くなることがあります。

1つの要因はローサイドFETスイッチング回路の追加損失で、この回路はローサイドFETのゲートの容量を充放電する電力を消費します。もう1つの理由は、非同期式デザインでは、逆方向インダクター電流はダイオードによって阻止されますが、同期式デザインでは、正負両方のインダクター電流が流れます。この負電流は、非同期回路では見られない追加の電力損失を発生させます。

同期式動作に必要な全ての信号レベルとタイミングを発生するコントローラーICが市販されています。多くの製品がハイサイドとローサイドの両方のFETまたはローサイドFETをパッケージに収めています。追加のタイミング回路は通常、コントローラーICに内蔵されており、FETをオンする頻度を減らしてスイッチング損失を減らすパルススキッピングによって、または負荷によって動作周波数を減らして、低負荷状態での効率を上げます。これらのことから、多くのDC-DCコンバーター設計では、非同期式より同期式トポロジーが一般的です。

2段の昇降圧(Ćukコンバーター)

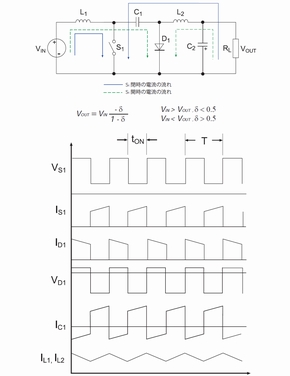

ĆuK(チュックと発音)昇降圧レギュレーターも、入力電圧をデューティサイクルによって、入力電圧よりも高いまたは低い安定化された反転出力電圧に変換します。図2の簡略図は基本回路図と関連した波形を示しています。これは簡単に言えば反転降圧コンバーターに容量結合した昇圧コンバーターです。

前に示したトポロジーに比べて、このトポロジーは2個のインダクターを必要とすることは簡単に分かると思いますが、両方のインダクターの電流は同じなのでコアを共有することができます。

スイッチS1が閉じると、電流IL1がL1を通ってVIN/L1のランプレートで流れます。同時に、C1の正端子は接地されているので、C1はL2を介して負電圧を放電してC2を再充電し、負荷RLに反転電流を供給します。

電流はL2を通って(VC1 + VOUT)/L2のランプレートで流れます。S1が開くと、L1に保存されているエネルギーがインダクターの電圧を上昇させ、D1を介してC1を再充電するのに使われます。

インダクターL1を流れる電流は(VC1 - VIN)/L1の減衰率で減少します。同時に、コンデンサーC2はL2とダイオードD1を通して放電するので、VOUT/L2の減衰率でL2の電流が減少します。

コンデンサーC1は入力から出力への全エネルギーの流れを負うので、ここでのこのコンデンサーの役目は特別です。定常状態の電圧が必ず一定になるようにC1の値を選択します。電流の方向により、出力電圧はグランド電位に対して負になります。従って、このトポロジーは負電圧を発生する場合にだけ使用します。このトポロジーの伝達関数の考察では、両方のインダクターの影響を検討する必要があります。

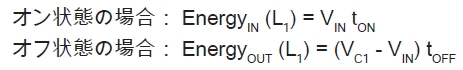

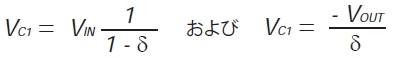

L1に関して適用される式は以下の通りです。

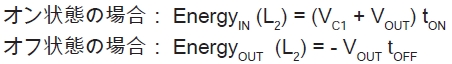

L2に関して適用される式は以下の通りです。

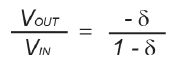

代入するとコンデンサーC1の電圧に関して2つの式が得られます。

これらを解くと、1段の昇降圧コンバーターの場合と同じ結果が得られます。

Copyright © ITmedia, Inc. All Rights Reserved.