差動信号伝送のメリット ――使用されている技術と注意点:高速シリアル伝送技術講座(2)(1/4 ページ)

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。

差動信号だからこそのメリットなのか?

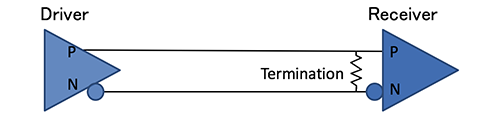

送受信1対1の差動伝送路の接続形態(トポロジ)では、図1のように2本の線(Positive/Nagative)を使用し、受信端で終端器を使用し接続します。

差動信号伝送は、PCなどのコンシューマーからHPCと呼ばれる先進的なハイパフォーマンスコンピューティングまで、通信や信号伝送が必要な用途で幅広く使用され、欠かせない技術となっています。差動信号のメリットとして一般的に、高速性、安定性、ノイズに強い、消費電力が低い、不要輻射ノイズが小さいなどが挙げられていますが、果たして差動信号だからこそのメリットなのでしょうか? 1つずつ検証していきましょう。

メリット1)差動信号は高速性に優れている

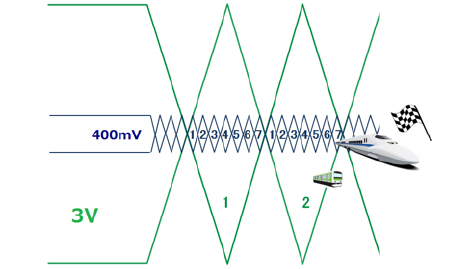

差動信号は大振幅のCMOS/TTLシングルエンドと比較すると小振幅で、エッジレートが同じ場合でも高速に動作します。図2の緑線はCMOS/TTLのおおよそ3Vの信号、青線は400mV振幅の差動信号を示しています。青線は緑線より7分の1ほど振幅が小さいために高速に信号をトグル可能です。受信側はアナログの差動増幅器を使用するため、小振幅を正常に受信できます。

小振幅の差動信号では、この組み合わせにより高速で安定した伝送が可能となっています。

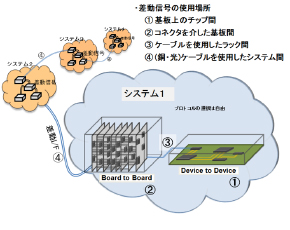

小振幅の基本的な優位性を利用し、外部、内部にかかわらず信号伝送が必要な部分では距離、スピード、トポロジに合わせてさまざまな形態や仕様の差動信号が使用されています。具体的には図3の①チップ間、②基板間、③シャーシ間、④システム間の電気信号接続部に使用されています。

インフラで使用されている光通信も、光モジュールへの入出力信号は図4のように差動信号の1つLVPECLが使用されています。

差動信号で代表的なLVDSではDC〜3Gビット/秒(bps)帯域までの物理層製品が販売されており、高速、長距離、低消費電力化が必要な信号伝送部分に使われています。またLVDSの派生のEIA/TIA-899 M-LVDS(Multi-Pint LVDS)ではシングルエンド信号で採用されるバス接続のトポロジをサポートし、同時に高速化を可能にしています。

小振幅を採用することで高速化が容易になりますが、さらに高速化を図るため、PECL(Positive Emitter Coupled Logic)やCML(Current Mode Logic)ではエッジレートを上げる方法が採用されています。

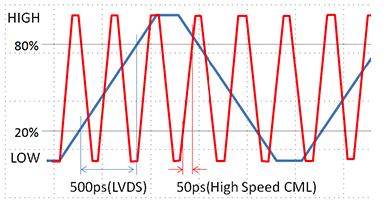

図5-1は、振幅が同じでエッジレートの異なる2つの信号を示しています(図では赤色と青色の線で表記)。青の信号は350mV振幅の一般的なLVDSドライバでエッジレートは500ps(tr/tf 0.5ns@20to80%)、赤の信号は高速なCMLでLVDSと同じ350mV振幅としています。

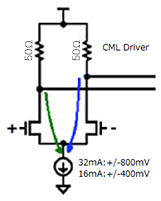

エッジレートを単純に比較すると赤は青より10倍高速で、同じ振幅でもエッジレートを上げることで単位時間当たりのスイッチング回数を増やし高速化を実現しています。今日では2値(バイナリ)のデータでCMLは28Gbps程度まで通信が可能です。しかし、PECLやCML(図5-2)では電流を多く流すことでエッジレートを高速化しているため、低電流源を採用するLVDSと比較すると、ずいぶんと消費電力が大きくなります。PECLやCMLは波形に含まれる高周波成分が多くなるため、伝送路のインピーダンス整合についてもより厳しい設計が必要となります。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:伝送路の要素。ドライバ、差動伝送路、終端抵抗器、レシーバー

図1:伝送路の要素。ドライバ、差動伝送路、終端抵抗器、レシーバー 図2:シングルエンド信号(緑)と差動信号(青)。振幅の違いによるトグルスピードの差

図2:シングルエンド信号(緑)と差動信号(青)。振幅の違いによるトグルスピードの差

左=図3:差動通信インターフェース / 右=図4:10G BASE-R SFP+ 光モジュール

左=図3:差動通信インターフェース / 右=図4:10G BASE-R SFP+ 光モジュール

左=図5-1:エッジレートの比較 LVDSとCML / 右=図5-2:CML ドライバ等価回路

左=図5-1:エッジレートの比較 LVDSとCML / 右=図5-2:CML ドライバ等価回路