差動信号伝送のメリット ――使用されている技術と注意点:高速シリアル伝送技術講座(2)(4/4 ページ)

メリット5)不要輻射ノイズが小さい

前述したようにCMOSロジック出力はスイッチング動作を行わない固定状態では、電流はほぼ消費されず放射ノイズも少ないですが、スイッチングでGnd・Vdd間に貫通電流が流れ、貫通電流が流れる周期の周波数で基板のGnd・Vddプレーンを揺らします。この動作が特定周波数でピークを持つ不要輻射ノイズの原因となります。

LVDS差動ドライバは図15-2の定電流源駆動の方式のため低消費電力で、CMOSロジック出力のスイッチング動作で起こる大きな貫通電流も存在していません。

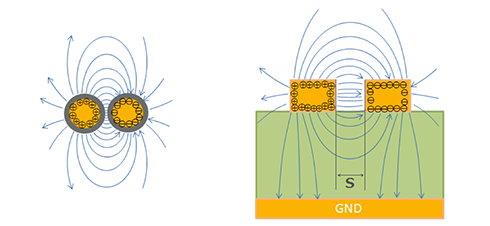

また差動の伝送では、図17のようにケーブルや基板上で2本の導体を電磁気的に結合し高速に信号を伝送しています。この差動間結合を強くすることで、放射されるコモンモードノイズを抑えることが可能です。

差動伝送路を設計する際は、+と−の2本の差動ライン間の距離(S)を狭くすることで結合を強くし、差動信号からの不要輻射を減らせます。ただしドライバ側の電源に入るノイズは、出力の差動2本にコモンモードノイズとして重畳され、不要輻射ノイズの原因となります。

第2回目は差動信号伝送に使用されている技術と半導体の動作を説明しました。複数の技術を組み合わせて、安定した高速伝送を行っていることが理解できたのではないでしょうか。

次回(第3回)は代表的な物理層であるLVDS、PECL、CMLと接続方法について説明していきます。

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

関連記事

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

本連載では、さまざまな高速通信規格に使用されている物理層の仕組みや性能、SerDesの機能や特徴とその種類、高速伝送での主要なパラメーター、伝送路を含んだ技術や設計手法などを分かりやすく解説していく。 HDMI 2.0のできること

HDMI 2.0のできること

映像/音声の伝送規格として定着したHDMIの最新規格「HDMIバージョン2.0」(以下、HDMI 2.0)がこのほど策定された。ここでは、これまでのHDMI規格バージョンとHDMI 2.0ではどのような違いがあり、どんなことができるようになったのかみていく。 SLVSインタフェースをFPGAで活用せよ

SLVSインタフェースをFPGAで活用せよ

SLVSは、データ信号を高速かつ低消費電力で伝送する用途において、LVDSに替わって利用される機会が増加しているデータ伝送規格である。FPGAにSLVSを実装する場合には、LVDSを実装する場合とは異なるさまざまな知見が必要になる。本稿では、SLVSの概要と、FPGAにおける応用例を紹介する。 長距離高速伝送が可能、LVDSインタフェース搭載のLEDドライバ

長距離高速伝送が可能、LVDSインタフェース搭載のLEDドライバ

ザインエレクトロニクスは、LVDSインタフェースを搭載したLEDドライバ「THL3512」「THL3514」を発表した。LVDSシリアルインタフェースを用いた制御により、高速・長距離伝送と高ノイズ耐性を可能にした。 インターフェースIC活用のススメ

インターフェースIC活用のススメ

ロジックICの電源電圧の低下に伴い、インターフェースICの重要性が増してきた。現在では、単なる負荷駆動の手段ではなく、より効率が良く、より安全な信号伝送の手段としてその価値は高まってきている。本稿では、まずインターフェース回路の基本を再確認した上で、各種インターフェースICの果たす役割や最新の製品動向を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

図17:差動結合 ケーブルとPCB

図17:差動結合 ケーブルとPCB