半導体(3) ―― 実際に経験した不良と対策(II):中堅技術者に贈る電子部品“徹底”活用講座(62)(2/3 ページ)

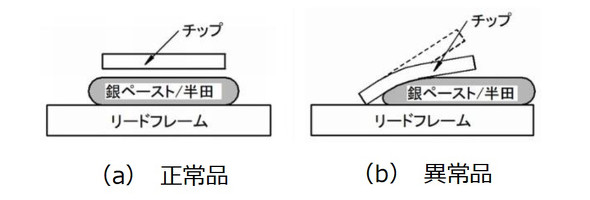

チップの歪み

組立工程では図3(a)に示すようにはんだや銀ペースト*などで個片のチップをフレームに固定します。この事例はフレームへの銀ペーストの塗布位置がズレたため、図3(b)に示すように銀ペーストの上に載ったチップが斜めになり、エポキシ成型時の応力でチップが歪んだものです。

半導体(Si)の共有結合は量子力学的な作用に基づくものですからチップが歪むと原子の電子軌道半径が歪み共有結合を成すことができません。結合できない電子はわずかな熱エネルギで伝導電子(キャリア)、つまり漏れ電流となって耐圧劣化の一因になります。キャリア数が限定されていますので定電流性のリークですが温度依存性を持ちます。

【対策】

銀ペースト塗布機のメンテナンス基準、出来栄え管理、抜き取り基準、などの管理条件の見直しを行い、頻度の適正化を図りました。

*銀ペースト:エポキシ樹脂に銀粒子を混ぜ、導電性を付与するとともに熱伝導度を向上させた接着剤

チップ品番間違い

セットのエージング工程において特定のトランジスタが焼損する事故が発生しました。調査の結果、チップデザインや損失に影響する特性曲線の様子が認定品と全く違うことからチップ品番と表示品番が異なっている、つまり異種混入であることが判明しました。

半導体メーカーでのチップ実装工程においてチップ保管箱の現品表示札を紛失したので、生産管理表から品番を推定しました。ですが生産予定品のVceo、hfeなどの特性値が片側規格であったり、誤品番の規格値とオーバーラップしていたりしたため違う品番のチップが実装されて出荷されてしまいセットにおいてトランジスタ焼損の事故になったものです。

またチップの工程間送り状が材料保管箱へのペーパーの投げ込みのみで紛失しやすく管理が不十分になっていました。

【対策】

工程間の員数管理法の改善/徹底、測定項目の追加、工程間送り状を紛失しない方法へ変更、片側規格から3σ管理への変更、などの対策を実施した。

チップ無断変更

海外メーカー製2チップ構成のパワーICにおいてパワ−MOSFETの焼損事故が発生し開封チェックを行ったところアバランシェ耐量不足により破壊、焼損したものと分かりました。

焼損前のMOSFETのチップを認定サンプルと比較するとチップそのものが全く違うデザインの未承認の小型化品に無断変更されていました。

未承認のMOSFETは同定格品ながら新しい技術で設計されて小型化が図られておりメーカーが無断でコストダウンが行ったものと分かりました。

この時点ではMOSFET自体の焼損事故の真因は不明でした。しかし当該メーカーの別稿の『特定条件下のアバランシェ耐量が著しく低下していた』という事例を経験した時点で焼損自体は同じ原因だったのではないかと推認しています。この時点では残念ながら時間的制約とチップを正規品に戻すという対策を行ったために真の原因を見過ごしてしまい、同社製品の採用見合わせまでには至りませんでした。

Copyright © ITmedia, Inc. All Rights Reserved.

図3:フレームへのチップ固定

図3:フレームへのチップ固定