次世代プロセッサはダイナミックな電圧制御と並列処理手法が決め手:スプリング・マイクロプロセッサフォーラム・ジャパン2006から(1/3 ページ)

消費電力を上げずに性能を上げるマイクロプロセッサが回路とアーキテクチャの2つの工夫で実現できる。回路的には動作状態に応じて電源電圧と基板バイアスをダイナミックに変える方法が主流になりそうだ。アーキテクチャ上はこれまでのメインフレームの実現に使われてきた各種の並列処理技術をプロセッサに応用するようになってきた。スプリング・マイクロプロセッサフォーラム・ジャパン2006では、このような方向がはっきり見えてきた。

消費電力を上げずに性能を上げるマイクロプロセッサを実現するには、ダイナミックな電圧制御と並列処理アーキテクチャが不可欠になる。6月8〜9日、ウェスティンホテル東京で開かれた「スプリング・マイクロプロセッサフォーラム・ジャパン2006」では、このような方向が明確になった。

決め手は細やかな電源オン/オフ制御

ルネサス テクノロジは、「組み込み用途向けマイコンの低消費電力ソリューション」と題した基調講演で、W-CDMA方式携帯電話機用システムLSIでの具体例を中心に、高い性能と低消費電力を両立させるための同社のこれまでの取り組みを明かした。その冒頭、演者を務めた同社システムソリューション統括本部システムコア技術統括部部長の長谷川 淳氏は、自動車のエンジン制御システムを例に挙げ、「1980年代以降、エンジン制御用のマイコンは10年間で20倍の性能向上を実現してきた。この経験則に従えば、2010年代には1GIPS(giga instructions per second)の性能が求められることになる」と説明。高性能化の実現には、トランジスタの閾(しきい)値電圧Vthを下げることと、微細プロセスの採用が必須だが、相反して、動作電流、リーク電流の増加を生んでしま

このような状況を受けて、ルネサス テクノロジでは、プロセスの進化に合わせて、集積度を上げるともに、新たな低消費電力化技術も順次盛り込んできた(表1)。ゲーティドクロック技術、電源のシャットダウンなどの工夫に続き、最近ではチップ上の各ブロックに電源を供給する領域を従来の5分割から20分割に増やし、動作中でも使用しない回路の電源をオフさせるよう細かく制御するようになった。

High-kゲート膜、動的制御

NECエレクトロニクスは、55nmプロセスに向けた低消費電力を実現する回路技術の詳細を明らかにした。

65nmプロセスとの大きな違いは、Vthと電源電圧(Vdd)を動的に制御する回路技術とHigh-k材料技術を組み合わせ、超低消費電力の実現を目指している点にある。55nmプロセスでは、65nmプロセスに比べ

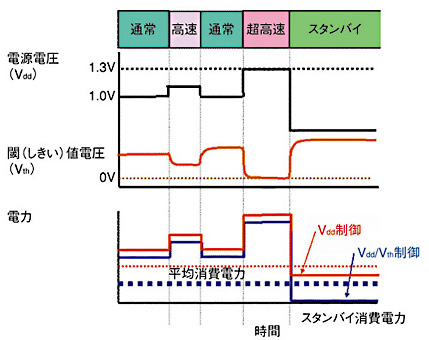

VddとVthを動的に制御する回路では、高速動作をさせたい時にはVddを上げ、Vthを下げる。また、低速動作時にはVddを下げ、Vthを上げる。必要な動作速度に応じてVdd/Vthを動的に切り替えること(図1)で、平均消費電力やスタンバイ消費電力を低減する。Vthは基板バイアスを変えることにより調整する。

ゲートリーク電流を下げるために導入したHfSiON(ハフニウムシリケード)膜は、Vthが上がるためドレインリーク電流を下げるという効果もある。

これらの回路技術を実装した組み込みプロセッサの消費電力比較評価では、電源電圧が1.2Vで動作時に160mWであった消費電力は29.4mWに、電源電圧が0.95Vで動作時に62mWであった消費電力は18.43mWにそれぞれ低減され、大幅な改善が見られたという。

基板バイアスでばらつきも低減

米Transmeta社は、MOSトランジスタの基板にバイアスをかけてVthを上げる技術やVddの最適化、クロック周波数の制限などの技術を駆使した、低消費電力技術LongRun2を用いたEfficeonプロセッサを開発、米AMD社にライセンス供与した。AMD社は現在、富士通のあきる野工場をファウンドリとして使い、300mmウェーハによる90nmラインで量産に入っていることを、明らかにした。

今回の技術は、基板バイアスをかけ、Vthを上げることによってサブスレッショルド電流を下げようとするもの。基板バイアスの効果はそれだけではない。Vthのばらつきも少なくなる。この結果、改良前と比べ消費電力は1/2.5に改善し、周波数特性も1.6倍改善した。例えば、700MHz動作では1W以下に、1.5GHz動作なら3.6W以下の消費電力を実現できる。Efficeonの試作品ではスタンバイ電力が8mWと小さかった。

パワーマネジメントで電力削減

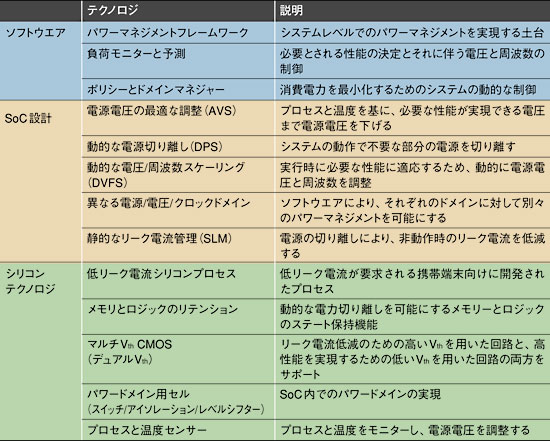

米Texas Instruments社がアプリケーションプロセッサ「OMAP3」の心臓部ともいえるF1プロセッサの消費電力を下げるために、パワーマネジメントをチップ設計、プロセスおよびソフトウエアの全体でとらえた「SmartReflex」と呼ぶ独自の技術を開発した(表2)。

これは「携帯電話機向けプロセッサでありながら、プロセッサを最大動作周波数で動かすことができる」(日本テキサス・インスツルメンツの筑波テクノロジーセンターでDSP開発部長を務める我孫子茂志氏)ようにするためだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

表1 省電力技術の進化 出典:ルネサステクノロジ

表1 省電力技術の進化 出典:ルネサステクノロジ  図1 ダイナミックな電圧制御方式 出典:NECエレクトロニクス

図1 ダイナミックな電圧制御方式 出典:NECエレクトロニクス  表2 TI SmartReflexテクノロジ 出典:日本テキサス・インスツルメンツ

表2 TI SmartReflexテクノロジ 出典:日本テキサス・インスツルメンツ