磁界測定の基本を押さえる:EMI対策への第一歩!

計測装置に代表される高性能機器の開発時には、ノイズ対策に注意を払わなければならない。例えば、システムの構築に必須のDC-DCコンバータが、EMIノイズの発生源となることは周知の通りだ。本稿では、DC-DCコンバータの磁界測定の実例を示しながら、EMI対策を行うために必要となる基本的な知識をまとめる。

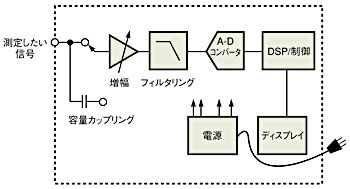

計測装置では、ノイズの影響を除去するために、信号処理経路の初期の段階で測定の対象となるアナログ量をデジタル値に変換するということがよく行われる。そのような計測装置には、帯域が広く、ノイズが少ない線形フロントエンド回路と、それと同等に高性能なA-Dコンバータが必要となる(図1)。その電源には、図のようにライン電源が使用されるケースもあるが、多くの場合はDC-DCコンバータが用いられる。

計測機器メーカーのウェブサイトを見ると、120dB以上のダイナミックレンジを実現している製品が並んでいることに気付く。ダイナミックレンジを広げるには、スプリアス信号の発生源となるものをすべて除去しなければならない。高性能な機器を設計するには、電源やデジタル回路などの一般的なノイズ源だけでなく、すべての潜在的なノイズ源の有無を調べる必要がある。

また、100dBを超えるようなダイナミックレンジが必要な場合には、信号対雑音比(S/N比)も高くなければならない。そのためには、例えば、FPGA内のチャージポンプ、プロセッサの起動/停止時に発生する温度変化、あるいはその機器の上に誰かが置いた別の機器から受ける磁気の影響といったことまで考慮する必要がある。高精度のアナログ回路を内部/外部の電磁波の影響から隔離することが、設計における重要なポイントとなるのだ。

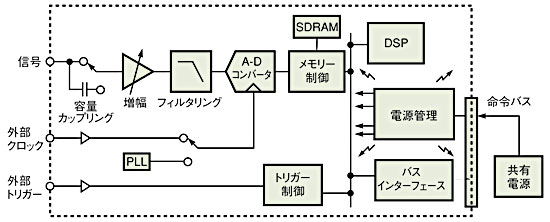

計測機器業界には、今、変革が起きている。性能指向型設計(performance based engineering)の時代を経て、市場では、各機器ベンダーに独自のアーキテクチャではなく、新しいオープンなアーキテクチャへの要求が高まっている(図2)。顧客は高性能が実現されていることはもちろん、オープンなアーキテクチャの利点も利用したいと考える。そのため、この新たな考え方を具現化するに当たっては、設計面での新たな課題が生じる。例えば、半導体のテスト業界では、SoC(system on chip)の検査に対応するため、テストシステムに含めなければならない機器の種類が急激に増加している。大規模なATE(automatic test equipment:自動試験装置)システムの市場投入までの期間とTCO(total cost of ownership:総所有コスト)を考えると、試験システムにはオープンなアーキテクチャが必要不可欠である*1)。

オープンなアーキテクチャを必要としているのはATEの分野だけではない。計測装置にオープンなアーキテクチャを採用すると柔軟性が高まるため、コストの削減、効率の改善、再利用性の向上、そしてサプライヤ間の競争の活性化が期待できる。

では、このような流れは、計測機器の開発チームにどのような影響を及ぼすのだろうか。性能指向型設計の時代には、開発チームはシステムのアーキテクチャの大部分をコントロールすることができた。しかし、例えばVXI対応のカードモジュラのようなオープンなアーキテクチャではそうはいかない。この種のアーキテクチャでは、バックプレーンのインターフェースと物理的なパッケージ構造が原因で、設計エンジニアは大きな制約を受けることになる。開発者は、機器の冷却、電力の変換などといった機器の周辺を取り巻く問題に、これまで以上に注意を払う必要がある。

そうした課題の中で特に重要なのが、計測システム内のDC-DCコンバータから発生するEMI(電磁波干渉)ノイズの抑制である。DC-DCコンバータは、システム内で電源が占める面積を削減し、電力供給にかかわる制約を緩和したが、ノイズの発生源になるという問題を抱えている。DC-DCコンバータの存在が、機器のSFDR(スプリアスフリーダイナミックレンジ)を制限してしまう可能性があるのだ。

ノイズの発生源は、対象とする機器内に存在するとは限らない。近くに配置された、同程度のダイナミックレンジ要件を必要としない別の機器がノイズの発生源となることもある。いずれのケースも、SFDRが劣化してしまう可能性がある。

計測機器は、内部にダイナミック電源が存在しようが、200MHzのデジタル出力ドライバの列があろうが、システム仕様を満たす必要がある。このような環境では、すべての部品をテストし、それらすべてが電界放射特性の要件を満たしていることを保証しなければならない。

磁気が及ぼす影響

近接場のEMIは、感度の高い計測機器に対してノイズの問題を引き起こす可能性がある。近接場には、ソースのインピーダンスに比例する電界と磁界が存在する*2)。空間/空気の377Ωという値よりインピーダンスの低い回路は、主に磁界を放射する。一方、高インピーダンスの回路は主に電界を放射する。

カップリングの仕方は、回路の構成や、存在する電磁界の状況によって異なる。代表的なものに、容量性のカップリングと相互インダクタンスによるカップリングがある。スイッチング電源の回路インピーダンスは低いことが多く、また電界は比較的容易にシールドできるので、本稿では磁気カップリングに焦点を当てることにする。

ファラデーの電磁誘導の法則から、回路の起電力と抵抗損失は、回路内の磁束の変化率に比例することが分かる。変化率がゼロなら、電圧は生じない。

磁気干渉は、周波数が高く、カップリングの度合いが強い場合に問題となる。磁束ΦMは、インダクタンスと電流の積として自己誘起する。あるいは、磁束密度とループの面積の積として相互誘起することもある(別掲記事「コンデンサとインダクタの類似点」を参照のこと)。

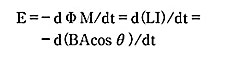

以下の等式が示す関係は興味深い。

ここで、Iは電流、Bは磁束密度、Lはインダクタンスを表す。

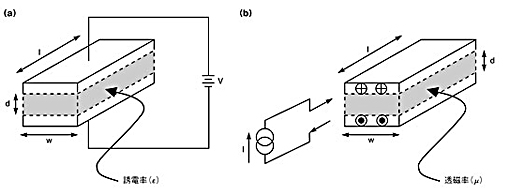

−d(BAcosθ)/dtについて補足しておくと、例えば磁界の測定を行う際には、プローブの先端にピックアップループを配置することになる。Aはこのループの面積であり、θはループの水平面と磁束の角度を表す(図3)。

この等式から、これらのパラメータを1つでも変化させると、回路に不要な電圧(エラー電圧)が生じることがわかる。電流、磁界、またはインダクタンスを変化させると、それに応じてエラー電圧が発生するということだ。

ノイズは、その発生源で抑えておくべきである。従って、計測機器の設計においては、機器に用いる部品を選択する前に、時間領域および周波数領域における近接場の特性を評価しておくとよいだろう。

DC-DCコンバータの実測例

先述したように、計測機器の開発では、システム内のDC-DCコンバータから発生するEMIの抑制が非常に重要である。しかし、磁界に関する性能はまだそれほど詳細に提供されていないので、個々の製品の特性を自身で評価する必要が生じるだろう。そこで、本稿では、仕様が似た2つのDC-DCコンバータの磁界放射に関する特性を、小型ループアンテナ(プローブ)を用いて評価する例を示すことにする。

ここで例にとる製品を、仮にX社、Y社の製品と呼ぶことにしよう。どちらも1/8ブリックのサイズで、35V〜75Vの広い入力範囲を持つ。出力電圧は5V、負荷抵抗は4Ωで同一である。変換アーキテクチャも同等で、広い入力範囲を実現するレギュレーション段の後に固定比率の絶縁段を備えており、同じ周波数で動作する。いずれの製品のスペックシートにも、磁気放射に関するデータは記載されていない。

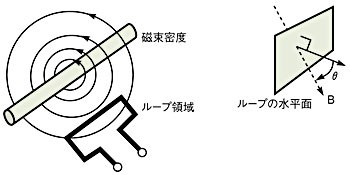

図4に示したのは、この特性評価に用いる評価系である。この評価系では、まず図の左側にあるプローブにより、DC-DCコンバータの上部の磁界を検知する(別掲記事「プローブの自作」を参照のこと)。プローブのアンプによって増幅された信号は、オシロスコープとスペクトラムアナライザに取り込まれる。信号のラインは、まずBNCを備える高インピーダンスのオシロスコープ入力部に入る。そして、スペクトラムアナライザの入力部が終端となる。DC-DCコンバータの磁気放射には、50MHz以上にもなるスイッチング信号からの広帯域エネルギーが含まれるので、測定に当たっては、信号の経路を高周波伝送線として扱うことが重要である。

プローブの先端は、DC-DCコンバータを実装しているプリント基板に平行に当てる(図5)。これにより、DC-DCコンバータの周辺に与える影響を調べる。具体的には、基板の表面をスキャンして、大きな出力が発生している個所を探し出す。その結果、磁界が最も強いのは絶縁トランス(絶縁段)の上であることがわかる。この測定は、トランス部の上面から0.65インチ(約1.65cm)上の位置で行う。これは、DC-DCコンバータを適切なスルーホール設計に組み込んだ場合に、マザーボードの表面となる水平面の1インチ(約2.54cm)上にプローブを当てることを想定しているためだ。

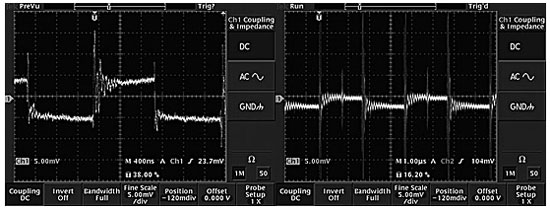

時間領域での測定結果からは、DC-DCコンバータの基本周波数とリンギング周波数が得られ、磁界の強度がどのくらいであるかが見てとれる(図6)。これらの結果から、DC-DCコンバータの磁気に関する設計にはトレードオフが存在することがわかる。絶縁トランスの漏れインダクタンスと磁化インダクタンスは、測定用のプローブと相互にカップリングする。X社の製品は測定時の基本磁界が高いことから、絶縁トランス内の磁化インダクタンスが非常に小さいことがわかる。一方、Y社の製品は漏れインダクタンスが小さいため、リンギング周波数が高い。スイッチング時に生じるリンギングは、漏れインダクタンスとスイッチの寄生容量に起因する。

図6 X社、Y社製品の時間軸での測定結果 両社の製品は、サイズや基本的なアーキテクチャ、スペックなどの面でほぼ同等である。しかしながら、X社の製品の測定結果(a)、Y社の製品の測定結果(b)を見ると、それぞれの上部に発生する磁界にはかなりの違いがあることがわかる。

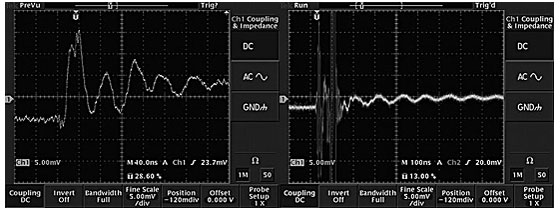

図6 X社、Y社製品の時間軸での測定結果 両社の製品は、サイズや基本的なアーキテクチャ、スペックなどの面でほぼ同等である。しかしながら、X社の製品の測定結果(a)、Y社の製品の測定結果(b)を見ると、それぞれの上部に発生する磁界にはかなりの違いがあることがわかる。 図7 X社、Y社製品の波形の詳細 X社の製品(a)およびY社の製品(b)のスイッチング特性は似ている。しかし、その詳細を見ると、Y社の製品の場合、磁化インダクタンスからの放射は全体的に小さいが、漏れインダクタンスにより高周波の共振が発生し、スイッチング時のピーク電圧が高いことがわかる。

図7 X社、Y社製品の波形の詳細 X社の製品(a)およびY社の製品(b)のスイッチング特性は似ている。しかし、その詳細を見ると、Y社の製品の場合、磁化インダクタンスからの放射は全体的に小さいが、漏れインダクタンスにより高周波の共振が発生し、スイッチング時のピーク電圧が高いことがわかる。前出の等式で示した関係を基に考えると、次のようなことがわかる。まず、方形波応答は、磁束が線形に変化していることを表す。また、DC-DCコンバータ内の磁気部品は線形領域で動作しており、電流は線形に増加している。具体的には、X社の製品の磁界は18μTppの三角波となっている(別掲記事「電圧と磁界の関係」を参照のこと)。

放射を減少させるには漏れインダクタンスが小さいほうがよいが、高周波での共振により大きなピーク電圧が発生する。スイッチング時の過渡特性を詳細に調べることにより、DC-DCコンバータ内の共振に関する情報を得ることができる(図7)。

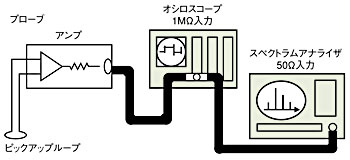

交流印加/測定装置におけるスペクトラム干渉に関心がある場合には、スペクトラムアナライザによって得られる情報が有用である。例えば、Y社の製品の磁界スペクトラムを広範囲で観測すると、10MHz辺りで共振が見られ、20MHz〜25MHzにピークを持つことがわかる(図8)。

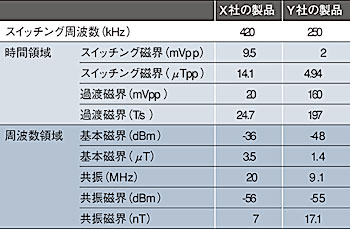

表1に、両製品の測定を通じて得られたデータを示しておく。両製品のスペックなどは似通っているが、磁界に注目すると、その特性には大きな違いがあることがわかるだろう。

詳細な評価が肝要

計測機器をオープンなアーキテクチャで実現するうえでは、DC-DCコンバータが重要な役割を担う。DC-DCコンバータが性能を妨げるノイズ源でないなら、オープンなアーキテクチャは、さまざまなアプリケーションのプラットフォームとして利用可能になる。

本稿では似通った2つの製品の評価結果を示したが、その結果から分かるように、各製品が発生する磁界がシステムに及ぼす影響はスペックシートを見ていただけでは判断できない。従って、オープンなアーキテクチャを用いて機器を開発する際には、性能を妨げない環境を保証するために、こうした部品の評価を注意深く行わなければならない。

コンデンサとインダクタの類似点

理想的な導体で構成された回路は、電気/電子エンジニアにとって非常に扱いやすい。それに対し、インダクタは磁気成分を持つこともあり、少し理解しにくいところがある。しかし、インダクタとコンデンサに類似性があることに気付けば、回路の動作が分かりやすくなるはずだ(図A)*。

コンデンサの極板間の電界強度Eは、電圧Vと極板間の距離dを用いてE=V/dで表される(単位はV/m)。一方、導体の磁界強度Hは、電流Iと導体の幅w(ループの長さ)を用いて、H=I/wとして表すことができる(単位はA/m)。

コンデンサの静電容量は極板の面積w×l、極板間の距離d、および極板間の物質の誘電率εにより、C=(εwl)/dで表される。ここで、誘電率εの単位はF/mである。極板間の距離が等しい場合、誘電率が高いほうが極板の面積当たりの容量値は大きい。

導体をループ状にしたものがインダクタだが、そのままでは扱いにくいので、ここでは図A-(b)のようにモデル化して考える。すると、インダクタンスの値はL=(μdl)/wで表すことができる。ここで、μは導体の周辺物質の透磁率で、単位はH/mである。透磁率が高いほうがインダクタンスは大きくなる。

コンデンサにおいて、電束はその空間中の全電荷量に等しい。つまり、コンデンサの電束Φは、容量Cと電圧Vを用いてΦ=CVで表すことができる。放電時には、コンデンサは電流源となる。

インダクタの磁束は、コンデンサの帯電量と似ている。磁束の単位はWbで、インダクタに電流を流すと、電圧が発生する。磁束ΦMは、ΦM=LIで表される。

容量に影響を与える誘電率は、電束密度、つまり単位面積当たりの電荷に影響を与える。コンデンサの極板の正電荷と負電荷の間の電束線について考えてみると、単位面積を横切る電束線の数はD=Φ/(wl)=εEとなる。これが電束密度である。式の通り、電束密度は誘電率に比例する。

インダクタの透磁率は、磁束密度に影響を与える。磁束密度は単位面積当たりの磁束であり、B=ΦM/(dl)=μHで表される。

*)参考文献

Walker, Charles S, Capacitance, Inductance and Crosstalk Analysis, Artech House, 1990.

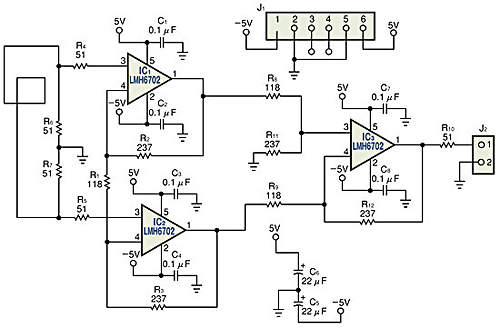

プローブの自作

図4に示した「プローブ」は「ピックアップループと「アンプ」により構成されている。その詳細は、図Aの通りである。この回路では、ピックアップループが生成した信号を広帯域のオペアンプによって約20dB増幅する。広帯域のオペアンプを用いる理由は、計測機器開発において最もケアすべきDC-DCコンバータが、25MHz〜60MHzの共振部品を持つためだ。

プローブの出力は、要件に応じて、スペクトラムアナライザまたはオシロスコープによって観測する。多くの交流印加/測定装置では、性能をSFDRで表す必要があるため、スペクトルデータに注目することが多い。一方、直流の測定ではノイズの総量(RMSパワー)が問題になるため、時間領域での電磁界測定を行うことが多い。

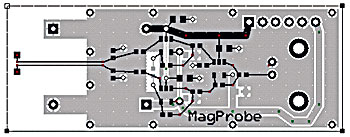

図B、図Cはそれぞれアンプ部の実装基板とピックアップループである。ピックアップループは、実装基板上の回路に対してループ部が垂直になるようにしている。ループ部の半径は、0.4インチ(約1cm)である。ピックアップループ部を平衡入力とすると、電界カップリングを打ち消すことが可能になる。また、実装基板のレイアウトは、できるだけバランスに配慮したものにする。

電圧と磁界の関係

計測機器の開発時には、磁気干渉の原因となるさまざまなソースの特性を評価する。その際には、電圧の測定値を磁界データに変換できると都合が良い。

測定の対象となる回路の電流は、ピックアップループを横切る磁束を生成する。磁界に対するピックアップループの角度θは固定だが、磁束密度Bは変化して|VMEASURED|=KAALcosθdB/dtで表される電圧が発生する。ここで、KAはアンプのゲイン、ALはピックアップループの面積(単位はm2)、dB/dtは磁束密度の変化率である(単位はWb/m2またはT)。本稿の例の場合、以下の式が成立する。

|dB/dt|cosθ=2467×VMEASURED

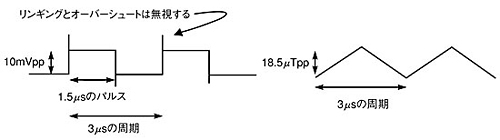

ここで、スイッチング部品から発生する電圧の値について考えてみよう。図Aのように、3μs周期でデューティ比が50%、振幅が10mVppの信号について考える。スイッチング動作の過渡時に発生するピーク偏差(オーバーシュートとリンギング)は、RMSパワーにはほとんど影響しないので無視することにしよう。この場合、5mVの片側ピーク電圧は、12.3T/sの磁束密度変化率に相当する。この変化率が1.5μs続くとすると、ピックアップループの方向の磁束密度は18.5μTppとなる。

磁界強度Hの単位は、A/mである。その値は、磁束密度Bの値を空間の透磁率4π×10−7で除算することにより得られる。37μTppの磁束密度は、空芯回路における磁界強度29.4A/mと等価である。

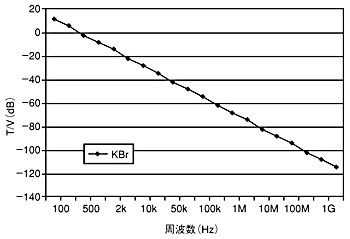

スペクトラムアナライザを使用すると、ノイズカップリングを別の角度から観測でき、リンギングや共振の問題について調べることが可能になる。例えば、稿末に挙げた参考文献*には、以下の式を利用する例が示されている。

VN(ω)=ωKAALBR(ω)cosθ

ここでVNおよびBRは対象とする周波数におけるRMS値であり、KAはアンプのゲイン、ALはピックアップループの面積、θは磁界ベクトルと、ループ領域に垂直な領域との間の角度である。この式から、周波数に対する磁束密度/電圧の関係を図Bのようなグラフで表すことができる。

*)参考文献

Ott, Henry W, Noise Reduction Techniques in Electronic Systems, Second Edition, pg 38, John Wiley & Sons, 1988.

脚注

※1…Perez, Sergio M, "The Critical Need for Open ATE Architecture," Proceedings of the International Test Conference, pg 1409, 2004.

※2…Ott, Henry W, Noise Reduction Techniques in Electronic Systems, Second Edition, pg 159, John Wiley & Sons, 1988.

Copyright © ITmedia, Inc. All Rights Reserved.

図1 計測装置のアーキテクチャ

図1 計測装置のアーキテクチャ  図2 計測装置のオープンなアーキテクチャ ブロック図レベルでは、オープンなアーキテクチャとベンダー固有のアーキテクチャに大きな差はない。しかし、実装レベルでの違いは大きい。

図2 計測装置のオープンなアーキテクチャ ブロック図レベルでは、オープンなアーキテクチャとベンダー固有のアーキテクチャに大きな差はない。しかし、実装レベルでの違いは大きい。

図3 ピックアップループと磁束の関係 磁界の変化が、ピックアップループに対して電圧を引き起こす。この電圧は、ループの面積とループの水平面に垂直な磁界成分の変化率に比例する。

図3 ピックアップループと磁束の関係 磁界の変化が、ピックアップループに対して電圧を引き起こす。この電圧は、ループの面積とループの水平面に垂直な磁界成分の変化率に比例する。 図4 磁界の評価系 ピックアップループの出力をアンプで増幅し、オシロスコープとスペクトラムアナライザに入力する。プローブから計測機器への経路で、正確な計測を妨げるようなスプリアス信号が発生しないように注意しなければならない。

図4 磁界の評価系 ピックアップループの出力をアンプで増幅し、オシロスコープとスペクトラムアナライザに入力する。プローブから計測機器への経路で、正確な計測を妨げるようなスプリアス信号が発生しないように注意しなければならない。 図5 測定を行っている様子

図5 測定を行っている様子  図8 Y社製品の周波数軸での測定結果

図8 Y社製品の周波数軸での測定結果  表1 X社/Y社製品の評価結果

表1 X社/Y社製品の評価結果  図A コンデンサとインダクタのモデル

図A コンデンサとインダクタのモデル 図A 図4のプローブの回路

図A 図4のプローブの回路 図B 図Aの回路の実装基板

図B 図Aの回路の実装基板 図C ピックアップループ

図C ピックアップループ 図A 電圧と磁界の対応

図A 電圧と磁界の対応 図B 周波数と磁束密度/電圧の関係

図B 周波数と磁束密度/電圧の関係