新世代パワーMOS FETの制御と保護:高性能デバイスの特質を最大限に生かす!(2/3 ページ)

フローティング構造の採用、レベルシフト回路の改良

IRS20955Sでは、ノイズアイソレーションの手法として、上述したのとは別の方法を用いている。

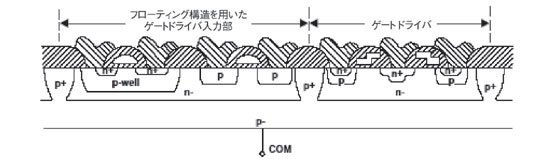

1つ目の工夫は、ゲートドライバへの入力回路部分が、ゲートドライバ回路に対してシリコン基板上でフローティングになるように構成していることである。これにより、ノイズの影響を軽減している。

フローティング構造は、図4のようにPN接合を逆バイアスすることで実現する(図中のCOM端子の電位を−VCCとする)。この構造であれば、グラウンド基準のPWM信号を直接ゲートドライバに入力することができるので、外付け回路は不要である。

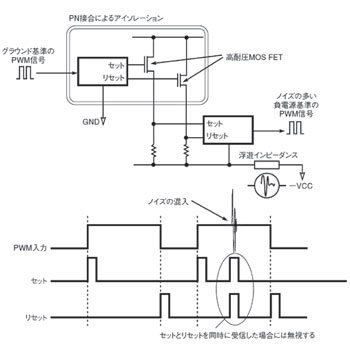

また、この方法では、フローティング構造を実現するPN接合をまたいでレベルシフトを行い、PWM信号を伝達することになる。ここに2つ目の工夫がある。

IRS20955Sでは、この部分に高耐圧MOS FETを用いる(図5)。図3に示したバイポーラトランジスタの回路例とは異なり、IC内部では入力されたPWM信号をセット/リセットの2つのパルス列に変換して電流モードで伝達する。このとき、2つのパルス列に、「2つが同時にハイになることはない」という約束事を決めておく。そうすれば、グラウンドと負電源との間に大きなスイッチングノイズが印可された場合でも、パルスを受け取る側は、それがノイズによるものなのか、本来の信号なのかを識別できる。つまり、2つの信号ラインが同時にハイの信号を受け取った場合、それは外来ノイズによるものだと判定され、その信号は無視されるわけだ。

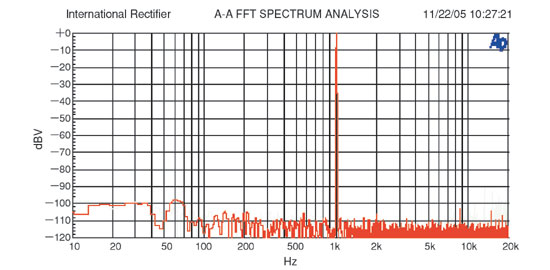

図6に示したのは、IRS20955Sを用いて構成したオーディオ用D級アンプの評価結果である。スイッチングノイズの影響を分離できた結果として、主信号に対し、低く良好なノイズフロアが得られている。このことから、上で紹介したノイズアイソレーション手法が、高周波化するスイッチングノイズの影響を排除し、信頼性の高いシステムを構成する上で重要な役割を果たすことが分かる。

過負荷からデバイスを守る

PWMアンプを利用した機器を開発する際に、出力段が破壊されてしまうという状況に遭遇することがある。そうなると、原因究明は容易ではない。出力段のMOS FETはスイッチング動作をするので、「少しだけオンさせてみる」という手法がとれないからだ。そのため、設計者は電源をオンするたびに壊れる出力段を前に、部品交換の続くデバッグ作業を余儀なくされる。

先述したように、新世代のパワーMOS FETは、単位面積当たりのオン抵抗が小さく、小さなシリコン面積でより多くの電流を流すことができる。面積が小さくなったことで、ゲート容量が小さくなり、同時に高速化も達成される。一見、良いことずくめのようにも思えるが、新世代のパワーMOS FETは、定格外の使用ではより短時間で破壊されやすいということに注目したい。なぜなら、小さなシリコンチップは熱容量も小さいからだ。

デバイスの保護という観点から見ると、新世代のパワーMOS FETは、より短時間で温度が急上昇しやすく、無理が利かない。従って、新世代のパワーMOS FETの保護回路には、素早く異常を検知して瞬時に出力を止められることが求められる。そのためには、過負荷検出機構の信頼性を高めることと、応答時間の短縮がキーとなる。

シャント抵抗はノイズ源!

ここで、一般的な過負荷検出の仕組みについて考えてみよう。

アンプ回路の出力段の損失は、トポロジーの違いにより、以下のように表される。

- リニアアンプにおける損失Pd

VCE:パワーデバイスにおけるコレクタ‐エミッタ間の電圧(電圧降下)

IC:パワーデバイスに流れるコレクタ電流

- PWMアンプにおける損失Pd

RDS(ON):パワーMOS FETのオン抵抗

ID:パワーデバイスに流れるドレイン電流

これらの式から分かるように、リニアアンプの損失は出力電流と出力電圧の両方によって決定される。それに対し、PWMを利用したスイッチングアンプの損失は負荷電流によって決まり、負荷インピーダンスや負荷電流の位相にはよらない。従って、PWMアンプの場合、負荷電流をモニターして過電流を検出することにより、過負荷保護回路を実現できる。つまり、誘導性の負荷(インダクタンスなど)を駆動するモーター制御用アンプやオーディオ用D級アンプなどでは、パワーデバイスの保護がリニア方式に比べて確実かつ簡単に行えるといえる。

過電流検出による過負荷保護回路の一般的な方法の1つは、電流検出用のシャント抵抗をデバイスに直列に挿入するというものである。しかし、MOS FETが高速化していくに連れ、シャント抵抗方式の過電流検出のデメリットが表面化してくることになる。シャント抵抗の浮遊インダクタンスの影響が顕著になってしまうからである。シャント抵抗の両端に発生するノイズ電圧は、抵抗を通過する電流の遷移速度(di/dt)の増加に伴い大きくなる。過電流検出用の電圧に加わるノイズ電圧が大きくなり、保護に用いる閾(しきい)値に達してしまうと、過電流保護回路が誤動作してしまうのだ。

ノイズによる過電流保護回路の誤動作を防ぐ方法の1つに、高周波成分を除去するLPF(low pass filter:低域通過フィルタ)を挿入してノイズ成分を除去するというものがある。しかし、この方法も問題を抱えている。

スイッチング周波数が高まると、シャント抵抗にノイズが現れる頻度が高くなり、通常の負荷電流との区別が難しくなる。これについては、ノイズ量の増加に対応してLPFの通過帯域を低く設定するという対策が考えられる。しかし、LPFは信号の伝達を遅らせるため、この対策では保護回路の応答速度を高めることができなくなってしまうのだ。

また、シャント抵抗の浮遊インダクタンスは、スイッチングスピードを低下させてしまう。それに加え、スイッチングに伴って不要なエネルギーを蓄積/放出することで、リンギングの発生によるEMI性能の劣化を引き起こす。さらに、外付けのシャント抵抗は、MOS FETのオン抵抗とともにジュール熱を発生し、効率の低下を招く要因にもなる。このように、外付けのシャント抵抗を用いることのデメリットは小さくない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図4 フローティング構造を用いたノイズアイソレーション

図4 フローティング構造を用いたノイズアイソレーション

図6 D級オーディオアンプの評価結果

図6 D級オーディオアンプの評価結果