D-A コンバータのINLを補正する:Baker's Best

D-Aコンバータを校正する際には、まず初めにフルスケール出力の1/3の点で入力コード対出力電圧の誤差を測定する。その次に、フルスケール出力の2/3の点で同じことを行う。このようにすれば、電源電圧付近での出力アンプの誤差を避けることができる。

オフセット誤差とゲイン誤差を補正するための式は、以下のように単純に表せる。

VOUT=a+b×VIN

この式において、aがオフセット誤差でbがゲイン誤差である。この式を用いた校正は、D-Aコンバータの目標性能よりも十分に高精度のA-Dコンバータを用い、デジタル演算の仕組みを設けることで行うことができる。これは、オフセット誤差とゲイン誤差が2LSBより大きい場合に有効な校正手法である。この2LSBという限界値は、A-Dコンバータの量子化誤差に起因する。

上述した校正手法よりも高度なものとして、D-Aコンバータの全出力範囲でのリニアリティを調整する方法がある。その場合もA-Dコンバータを使用するが、その分解能はD-Aコンバータの分解能の4倍以上も高くなければならない。それでも、D-Aコンバータの各コードに対して校正できるという点がこの方法の魅力だといえる。

この手法は8〜14ビット程度のD-Aコンバータに適用可能であろう。このくらいであれば、入力コード数が少ないため所要メモリー量が少なくて済み、またA-Dコンバータに要する精度も適度であるため高速な変換も可能である。14ビットを超えるD-Aコンバータにこの手法を適用しようとすると、入力コード数が多く、プロセッサの演算能力やメモリー容量を超えるほどの処理が必要になる。さらに、このような用途に使えるほど高精度で高速なA-Dコンバータはコスト面の問題で使用しづらい。従って、分解能の高いD-Aコンバータに対してこの手法を適用するのは現実的でないと判断される。

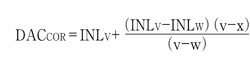

上述した方法に代わる効果的な手法として、いくつかの部分コードを使用するというものがある。D-Aコンバータの補正コードを計算する一般式は以下のようになる。

ここで、INLV、INLWはそれぞれコードV、Wに対応するINL(積分非直線性:integral nonlinearity)誤差、xはコードvとコードwの間に存在するコードである。v−wが2のべき乗に相当する整数の場合、割り算が右シフト演算で行えるため、プロセッサによる演算時間を短縮し、構成を簡単にすることができる。

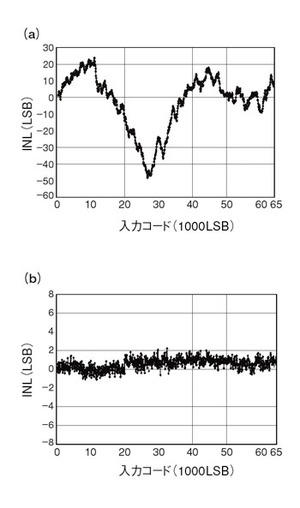

図1(a)に示したのは、16ビットの抵抗ストリング型D-AコンバータのINLの評価結果である。16ビットの抵抗ストリング型D-Aコンバータは216個の抵抗から構成され、アナログ信号を65536LSBで表現する。このD-Aコンバータに上述した方法を適用し、16ビット全体を1024分割して64LSB単位の部分コードごとに線形補正した場合、図1(b)のような効果が得られる。この方法は誤差の特性が単調で、INL誤差が±8LSB以上の場合に最適である。

上述した方法では、部分コードのコード数を選択する際に十分な注意を要する。コード数が多すぎると、あるコードとその次のコードの間にR2R方式D-Aコンバータで発生するのと同様なコード間ジャンプが生じ、補正を行うことにより、かえって特性が劣化してしまうこともあるからだ。抵抗ストリング型D-Aコンバータは単純な仕組みで動作し、ほかの方式のD-Aコンバータに比較してコード間でのジャンプが小さい。そのため、この補正方式に適している。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

Copyright © ITmedia, Inc. All Rights Reserved.

図1 16ビットD-AコンバータのINLの測定例 製品によっては、INLが10LSBオーダーになることがある。64LSBごとに補正を行うことより、そのINLを±3LSB以下に低減できる。

図1 16ビットD-AコンバータのINLの測定例 製品によっては、INLが10LSBオーダーになることがある。64LSBごとに補正を行うことより、そのINLを±3LSB以下に低減できる。