組み込み不揮発性メモリーの正しい選択(1/3 ページ)

SoCに組み込み可能な不揮発性メモリーにはいくつかの種類がある。それぞれの特徴をつかみ、用途ごとに求められる要件を吟味した上で最適なものを選択することが肝要である。本稿では、その選択のためのガイドを提供する。

多種多様な組み込みNVM

不揮発性メモリー(NVM:non volatile memory)を組み込んだICの需要が高まりつつある。この傾向を後押ししているものの1つは、MP3プレーヤなど、デジタル著作権管理やセキュリティ対策を必要とする民生機器の普及である。また最近の技術の進歩によって、設計者がさまざまな方法でNVMをオンチップに統合できるようになったことも背景の1つとなっている。

少量のNVMしか必要としないSoC(system on chip)の場合、一般にはマスクROMやバッテリバックアップ式のSRAM、アンチヒューズメモリーなどが使われることが多い。設計によっては、EEPROMやフラッシュメモリーが選ばれることもあるだろう。あるいは、ロジックNVM(ロジック回路用の通常のCMOSプロセスで製造可能なNVM)という選択肢もある。

こうした方式には、それぞれどのような長所/短所があるのだろうか。また、その選択が、システムのパフォーマンスやチップのコスト、テスタビリティなどにどのような影響を及ぼすのだろうか。自らの設計に最適なものがどれであるのかを知るには、SoCにおける各NVMの可用性とトレードオフについて知っておかなければならない(各種NVM技術については、別掲記事『さまざまなNVM技術』を参照されたい)。

NVMの適用個所

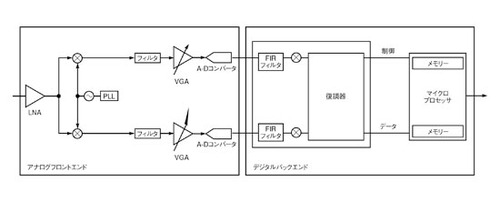

ここでは各種NVMを比較するために、RF受信システムを例として取り上げる(図1)。少し考えただけでも、組み込みNVMのいくつかの利用方法が浮かんでくるだろう。

アナログフロントエンドでは、アナログ信号がLNA(低ノイズアンプ)に入り、続いてミキサー、フィルタ、A-Dコンバータへと進む。一方、デジタルバックエンドでは、データがマイクロプロセッサに到達するまでに、フィルタリング、ミキシング、復調などの信号処理が行われる。この例では、デジタルバックエンドにおいて、1つの信号パスで制御に対応し、もう1つの信号パスでデータを扱うものとしよう。マイクロプロセッサは、アプリケーションで必要な操作をデータに対して施し、次段に送ることとする。

このようなRF受信システムのどこにNVMを使うと、パフォーマンスを向上させ、設計を簡素化することが可能になるだろうか。その可能性は至るところにある。例えば、アナログフロントエンドで少量のNVMを使うことで、LNAのゲイン調整、ミキサーにおけるトリム処理、PLL(phase locked loop)のフィルタ調整、アナログフィルタの係数変更、ゲインと位相の調整、A-Dコンバータのトリムなど、さまざまなところで精度を確保することができる。

製造プロセスが変わればアナログコンポーネントの特性も変化する。それに対し、NVMを利用してパラメータを変更できるようにしておけば、回路を常に適切に動作させることができる。また、温度の変化もアナログ回路の動作に影響を及ぼす。これについても、温度変化の激しい条件下では、MTP(multiple times programmable:何度でも書き込みができる)のNVMや、OTP(one time programmable:一度だけ書き込みができる)のNVMをベースとしたパラメータのルックアップテーブルを追加することで、システムの精度を維持できよう。

デジタルバックエンドでは、バス幅が広いほど、必要となるNVMの容量は大きくなるはずだ。例えば、DSPブロックにはフィルタ係数や復調パラメータ用の記憶領域が必要かもしれない。データがマイクロプロセッサに到達したら、頻繁に変更されるキーを使った復号化や、フレームの同期化、あるいは小規模なコードを更新してそれを格納するといったことが必要となるかもしれない。こうしたデータ関連の要件は、データがいつ、どのように更新されるのかということと、そのサイズや更新の理由によっても変わってくる。

表1に、このRF受信システムにおけるパラメータとNVMに求められる要件などをまとめた。

さまざまなNVM技術

組み込みNVMを利用する場合、設計者は、通常のCMOSプロセスにどれだけのマスクステップを追加しなくてはならないかを評価する。ロジックNVMのように追加マスクが不要のものもあれば、SONOSフラッシュメモリーのように2〜4枚の追加マスクを必要とするもの、フラッシュメモリーのように2〜10枚の追加マスクを必要とするものもある(フラッシュメモリーには通常2層のポリシリコンが必要であり、3つ目のポリシリコン層が必要とされる場合もある)。どれを選択するかは設計者次第だ。

シリサイド系のヒューズを使うNVMでは、記憶素子としてポリレジスタが使われる。設計者がデバイスをプログラムする際に約10mAの電流を流すことで、シリサイドの自己加熱とエレクトロマイグレーションが発生し、フィールド酸化膜上でポリヒューズの部分の抵抗が大きくなる。値を読み出す際にはMOS FETをオンにし、センスアンプがその状態を検出する。ヒューズ部分の抵抗値の増加により、記憶素子の状態変化が判別される仕組みだ。ヒューズ回路には一度しかプログラミングできないという制約があるし、プログラミングに要する電流が大きいため比較的大きなセルが必要となり、また信頼性の面での問題も起こり得る。

記憶素子として、オキサイドコンデンサが使われるNVMもある。このタイプのものでは、プログラミングの際、ストレスノードに大きな電圧を印加すると酸化膜が破壊されてしまうという問題がある。

大半のEEPROMとフラッシュメモリーには、フローティングゲート技術が利用されている。フローティングゲートのトランジスタは、荷電していない状態で製造されるか、紫外線を用いて電荷を消去した上で使用する。このフローティングゲートのトランジスタは、ホットキャリアの注入によりオンになる。

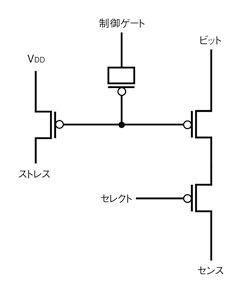

MTPのロジックNVMでも、フローティングゲート技術を利用する。マスクやプロセスステップを追加することなく、標準的なCMOSプロセスでセルを実装できる点が最大の特徴だ(図A)。プログラミング時には、制御ゲートをグラウンド電位で保持したままトンネルトランジスタのゲートを高電位に引き上げることでFN(Fowler-Nordheim)トンネリングが発生し、フローティングゲートの電荷が消去される。制御ゲートを高電位に引き上げ、残りのノードをグラウンド電位で保持すれば、FNトンネリングを逆方向に働かせることになり、ゲートに電荷がチャージされる。ストレスノードからのホットキャリア注入によってセルをプログラムすることも可能である。

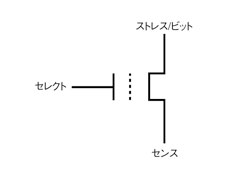

組み込みEEPROM/フラッシュメモリーでは、2重ポリシリコンを使用してフローティングゲートに電荷を蓄積する仕組みが用いられる(図B)。プログラミングの際には、ストレス/ビットノードを高電位に引き上げ、セレクトノードをグラウンド電位または負の電位とすることでFNトンネリングを発生させる。これにより、フローティングゲートの電荷を消去する。セレクトノードを高電位に引き上げ、残りのノードをグラウンドで保持してFNトンネリングを逆方向に作用させれば、フローティングゲートに電荷が注入される。ストレス/ビットノードからのホットキャリア注入によってもセルをプログラムできる。

SONOSフラッシュメモリーもフローティングゲートを利用するフラッシュメモリーと同じような方法で動作する。ただし、電荷の蓄積にはフローティングゲートの代わりに窒化物の層が使用される。一般に、SONOSはフローティングゲートを利用したNVMよりも低い電圧でプログラミング/消去が行える。フローティングゲートを用いたNVMの製造には、6〜10のマスク追加が発生するが、SONOSフラッシュメモリーでは通常のCMOSプロセスに2〜3のマスク追加を行うだけで済む。

Copyright © ITmedia, Inc. All Rights Reserved.

表1 パラメータとNVMに求められる要件

表1 パラメータとNVMに求められる要件 図A ロジックNVMのセル構造

図A ロジックNVMのセル構造  図B 2重ポリシリコンの利用法

図B 2重ポリシリコンの利用法