組み込み不揮発性メモリーの正しい選択(3/3 ページ)

周辺回路の影響

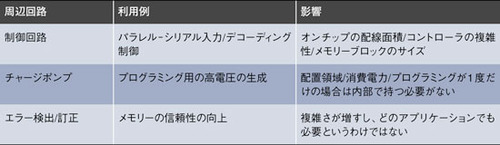

検討すべきもう1つの項目に、周辺回路のオーバーヘッドがある。どの組み込みNVMにも制御信号とデコード回路が必要であり、その複雑さはメモリーアーキテクチャによって異なる。

チップ内部に高電圧の電源ラインがない場合、プログラミング用の電圧を得るためにチャージポンプが必要になることもあるだろう。また、耐久性の高いメモリーが必要なケースでは、誤り検出/訂正機能と、ある程度の冗長性がセルに要求される。さらに、NVMのデータ消去方式によっては、過剰消去の問題を回避するための特別な制御回路が必要になるかもしれない。

メモリーIP(intellectual property)を利用する場合には、メモリーの周辺部についてしか把握することができない。設計者がオーバーヘッドを気にする理由は、特定のベンダーから入手した組み込みNVMが、チップ設計だけでなく基板の設計とコストにも影響を与えるからである。

表4に、周辺回路に関する影響に関して簡単にまとめておく。

選択に当たっては十分な検討を

組み込みNVMを利用する場合、システムの精度の確保、基板コストの削減、基板の複雑さの低減、テスタビリティの向上、エラーの訂正、フィールドでのプログラマビリティの確保、セキュリティの向上といった数々のメリットが得られる可能性がある。さらに、汎用CMOSプロセスが利用できれば、消費電力、チップコストを低減することも可能になる。

設計者は、まず自らの設計に必要なNVMの種類と容量について考えなくてはならない。NVMに求められる要件が分かったら、読み出し速度、設計の移植性、フィールドでのプログラマビリティ、消費電力、チップ面積などをコストに照らし合わせて評価する。その情報に基づけば、最適なIPベンダーを選択することも可能になる。組み込みNVMに対する理解が深まるに連れ、適切に機能する設計と、一応機能はするものの、市場ではすぐに失敗する設計との違いが分かってくるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

表4 周辺回路の影響

表4 周辺回路の影響