組み込み不揮発性メモリーの正しい選択(2/3 ページ)

チップ構成の検討

メモリー要件を4Kビット未満、最大256Kビット、256Kビット以上の3つのカテゴリに分けたいとする。そうすると、システムをいくつかに分割して考えることになるだろうが、その際には、製造時にプログラミングする(データを書き込む)サイズや、チップを実際に使用しているときに変更することになるサイズなども考慮して分割すべきだろう。

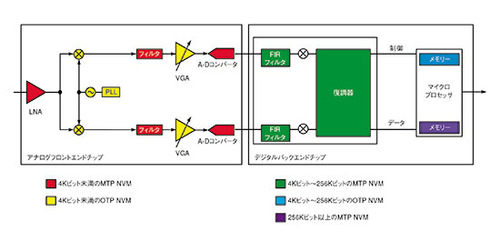

例えば、図1のRF受信システム(ミックスドシグナルシステム)は、図2のような2つのチップで構成する方法が考えられる。アナログフロントエンドチップでは、必要とされるNVMの容量は少なく、種類としてはOTP NVMが求められる傾向にある。一方、データバス幅が広いデジタルバックエンドチップでは、より多くのMTP NVMが必要とされる。大規模なコード/データの更新などに多くのNVMを必要とするアプリケーションでは、外部NVMへのインターフェースを用意したいケースもあるだろう。

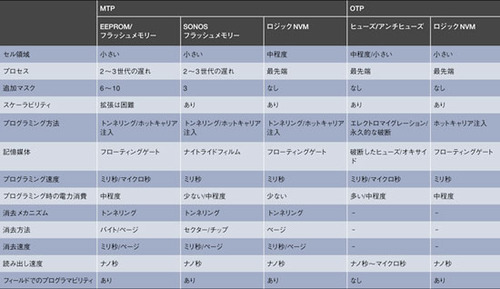

システムの統合を進めつつ、コストを削減し、スケーラビリティを維持するにはどのような選択をすればよいだろうか。この問いに答えるには、まずNVMごとの特徴を知る必要がある。表2に、各種NVMの比較をまとめた。なお、この比較には強誘電体RAMと磁気RAMは含まれていない。

特徴を押さえたら、次のアプローチにはいくつかの選択肢がある。例えば、以下の2つである。

- 2チップ構成でそれぞれを最適化

- 1つのミックスドシグナルチップを構成

以下、それぞれについてより詳細に考察を進める。

2チップ構成での最適化

まず、2チップ方式でそれぞれの設計を最適化する方法について考える。アナログフロントエンドの少量のメモリーとしては、アンチヒューズのOTP NVMを使ってもよいだろう。その場合、消費電力は多くなるが、OTPのロジックNVMを使うよりもプログラミング速度を高めることができる。量産用の設計の場合には、プログラミング速度が重要なコスト要因になる可能性がある。ただし、フィールドでのテストとプログラマビリティが必要とされる設計の場合には、ロジックNVMが最有力の選択肢となるだろう。アンチヒューズのNVMの場合、工場でプログラミングする必要があるからだ。

パッケージの特性も精密なアナログ部品に影響を及ぼすことがある。パッケージング後にプログラミングするほうが望ましいケースもあり、その場合の有力な選択肢もロジックNVMとなる。いずれにせよ、メーカーが最先端のプロセスでチップを開発し、余分なマスク費用がかからなければ、全体的な生産コストが下がり、信頼性も高まる。マスク枚数が増えると、回路内のすべてのトランジスタに影響が及ぶ。また、製造プロセスのステップが増えれば欠陥も増え、歩留りと信頼性が低下する。

一方、デジタルバックエンドチップには、組み込みNVMとしてEEPROMかフラッシュメモリーが使用されることが多い。これらは、外部メモリーに代わる自然な選択肢だといえよう。データストレージ用のメモリーをチップに組み込めば、I/O回路を減らすことができる。また、外部コンポーネントがなくなることで、システムの部品コストも削減可能になる。さらには、配線数が少なくなるため基板コストが下がり、読み出し速度も向上する。

組み込みEEPROM/フラッシュメモリーを利用すれば、消費電力を低く抑えられる。しかし、EEPROM/フラッシュメモリーをチップに搭載すると製造プロセスのステップが6〜10も増えることになる。その影響が大きすぎると会社が判断すれば、話は振り出しに戻ることになる。消費電力を減らし、かつプロセスへの影響が少ない方法を模索していけば、SONOS(silicon oxide nitride oxide silicon)フラッシュメモリーという選択肢に行き着くかもしれない。これならば、マスクが3枚ほど増えるだけで済む。

1チップ化する場合の選択肢

続いて、1つのミックスドシグナルチップにメモリーを統合する方法について考える。この場合も、フィールドでのテストとプログラマビリティが必要なら、ロジックNVMが最有力の選択肢となるだろう。

デジタルバックエンドにおいて、中程度のサイズ要件に対してロジックNVMを使用すると、面積と速度が犠牲になるものの、コストが低下し、大抵は歩留りが向上する。ロジックNVMを採用することで設計全体が1つのプロセス(汎用のCMOSプロセス)に収まり、プロセスステップが増えることはない。汎用のCMOSプロセスが利用できるということは、設計の移植性の向上、消費電力の削減、最先端プロセスへの移行が可能といったメリットにもつながる。

なお、マイクロプロセッサが数メガビットのMTPメモリーを必要とするなら、組み込みEEPROMまたはフラッシュメモリーに選択肢が限定される。デジタル部分では、SONOSフラッシュメモリーを使用するほうが、組み込みEEPROMを使用するよりも消費電力が少なくなる。

表3に、設計上の主なトレードオフをまとめておく。

Copyright © ITmedia, Inc. All Rights Reserved.

表2 各種NVMの比較

表2 各種NVMの比較 表3 設計上のトレードオフ

表3 設計上のトレードオフ