HDビデオエンコーディングのアーキテクチャ:DSPとFPGAの最適な併用法を知る(2/2 ページ)

SRIOの効用

ビデオ会議アプリケーションでは、エンコーダに対する要求はさほど高くない。それに対し、ビデオ放送のエンコーディングでは、ビデオ会議アプリケーションのエンコーダとは異なる周辺ブロックが必要になる。

ハイエンドのエンコーダでは、チャンネル当たりのコストを低く抑えつつ、高いチャンネル密度とスループットを実現する必要がある。適切な周辺ブロックとメモリーを組み合わせれば、この目標を達成することができる。DSPおよびFPGAを用いたアーキテクチャでは、広帯域幅を持つ周辺ブロックが重要となる。それがあれば、複数のDSPを使用することにより、高性能アプリケーションの実現が可能になる。

例えば、500MHzのDDR2外部メモリーインターフェースでは、前世代のDDRに対してスループットが2倍となった。そのため、迅速なデータ転送が可能になった。この手法は、2MバイトのL2キャッシュメモリーを提供することにより、性能を上げ、インフラアプリケーションにおける1チャンネル当たりのコストをさらに引き下げた。またGigabit Ethernet MAC(media access controller)は、前世代の機器の10倍の帯域幅を有する。

こうした例と同様に、DSP上でSRIO(serial rapid input/output)バスを使用すれば、スイッチングやプロセッサのアグリゲーションのための追加デバイスが不要になるため、システム全体のコストを削減することができる。またSRIOによる相互接続は、ピアツーピアで高速なパケット交換を可能とし、マルチプロセッサを用いたマルチチャンネル実装によって性能を画期的に向上させる。1レーンのSRIOリンクにより、デバイス間で1080iのビデオデータを送信することができる。4レーンならば、帯域に余裕を持って1080pのビデオデータを転送することも可能である。インフラアプリケーションでSRIOを使用することにより、デバイス数、基板面積、デバイスコストを低減し、システムコストを大きく削減することができる。

SRIOがチップ間接続を実現する唯一の方法というわけではない。しかし、PCIやEMIF(external memory interface)などの従来のチップ間接続手法と比較して、SRIOにはいくつかの利点がある。例えば、PCIの帯域幅が133メガバイト/秒であるのに対し、4レーンのSRIOでは1250メガバイト/秒を実現する。また、PCIがサポートしないメッセージ送信やマルチキャストをSRIOは直接サポートする。さらに、EMIFでは端子数が約90本であるのに対し、SRIOは16本しか使用しない。SRIOはマスター‐スレーブ間のインターフェースとしてシームレスな接続をサポートし、堅牢なプロトコルと帯域内割り込みを実現する。

SRIO以外の従来のインターフェースでは、帯域幅を拡大することはできない。そのため、必要な性能を達成するには複数のパラレルインターフェースを用意する必要があった。また複数のデバイスでバスを共有すると、入出力性能が著しく低下する。マスターまたはスレーブとして動作可能なインターフェースは存在するが、両方の役割を果たすことはできない。そのため、追加のシステムサポートやグルーロジックが必要になる。

SD/HDをサポートするアーキテクチャ

広帯域幅のI/OブロックをDSPに集積すれば、別の設計オプションを考えることができる。ビデオ放送用のリアルタイムHDエンコーディングに必要なメモリー帯域幅を満たすDSPがあるなら、ほとんどの場合において、DSPとFPGAを組み合わせた複雑な構成よりも、複数のDSPを使用することを考えたほうがよい。チップ設計者らがチップ間通信の問題を解決してくれていることが、HDエンコーディングに2つのDSPを利用しようと考える主な理由となる。拡張性があることも、DSPを利用することの魅力の1つだ。HDの普及はまだ始まったばかりなので、少しの手間でHDに拡張可能なSD(標準解像度)を提供するほうが実用的であるケースは多い。高性能なI/Oを搭載したDSPを採用すれば、その移行は容易である。

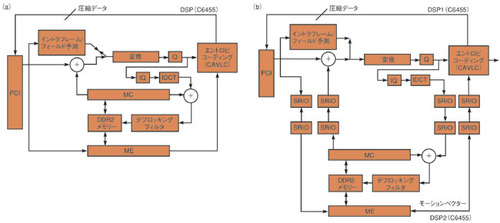

まず、SDビデオのエンコード手法を考える。周辺ブロックが充実した1GHz動作のDSPならば、H.264/AVC Baseline Profileを、720ピクセル×480ピクセルの解像度、30フレーム/秒でエンコードできる(図4)。この場合、MCはオンチップで実行する。エンコーディングでHDが要求されるようになったら、言い換えれば1280ピクセル×720ピクセルの解像度、30フレーム/秒が求められるならば、1GHzで動作するDSPを2つ用意し、プロセッサ間通信にSRIOを用いればよい。このとき、MEおよびMCは、もともとSDエンコーディングを実行していたチップではなく、2つ目のDSPで行う。どちらの設計においてもFPGAによる補助は不要である。

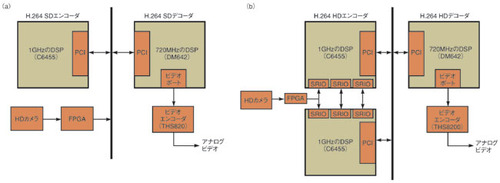

エンコーディング/デコーディングを同時に実行するアプリケーションへと設計対象が変わっても、その処理のほとんどをDSPで実行することが可能だ。エンコーディング/デコーディングを同時に行うには、図5(a)のような構成とする。720MHzのメディアプロセッサにおけるSDデコーディングと、1GHzのDSPにおけるSDエンコーディングに対応し、カメラからの映像をFPGAでバッファするようにしている。HDエンコーディング/デコーディングが必要なシステムなら、図5(b)のように、低コストで高性能なメディアプロセッサとFPGAを用いたアーキテクチャを採用すればよい。

図5(b)のHDシステムは、H.264/ AVC Baseline Profile、HDエンコーディング、HDデコーディングを、1280ピクセル×720ピクセル、30フレーム/秒で同時に実行することができる。SRIO付きのDSPは、チップレベルの相互接続と、最大10ギガビット/秒の全二重相互接続のプロセッサ間通信を提供する。また、同一ボード上にSRIO付きDSPを複数使用することで、マルチプロセッシングアーキテクチャの実装が容易になり、演算上のボトルネックが生じないことを保証できる。並列に動作する1GHzのDSPを10個搭載したボードであれば、10GHz相当の性能を実現可能だ。そうしたボードは、SRIO、HD SDI(serial digital interface)、CameraLinkなど、複数のI/Oモジュールをサポートするように設計できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング