低消費電力LSIの設計技術:最新技術動向をまとめて理解!(1/5 ページ)

携帯型端末などに用いるLSIには、当然のことながら、低消費電力化の実現が要求される。しかし、昨今では、それ以外の用途に向けたASICやSoCを設計する場合でも、低消費電力設計手法の適用が必須となっている。最新のプロセス技術を用いると、必然的にリーク電流が多くなってしまうからだ。本稿では、ASIC設計者が知っておくべき、消費電力の削減手法についてまとめる。

つい最近まで、LSI設計における低消費電力化は、必ずしもすべてのLSI設計者に必須の技術だとはいえなかった。しかし、130nm以下のプロセス技術をターゲットとしてASIC(application specific integrated circuit)やSoC(system on chip)を設計する場合には、ほとんどのLSI設計者が低消費電力化を実現するための設計技法を習得する必要が生じてくると予想される。ファウンドリでは130nm以下の製造プロセスにLow-k(低誘電率)材料、銅配線などの新材料や新技術を採用し始めており、それよってLSIのゲート当たりの面積は縮小し、動作は高速になった。しかし、メリットだけではなく面倒な副作用も生じることとなった。それは、リーク電流による消費電力(以下、リーク電力)の問題である。この問題に対処するために、90nmの製造プロセスにおいてはパワーマネジメント技術の導入が必要で、65nmの製造プロセスでは消費電力を削減するための各種設計技法が必須となった。

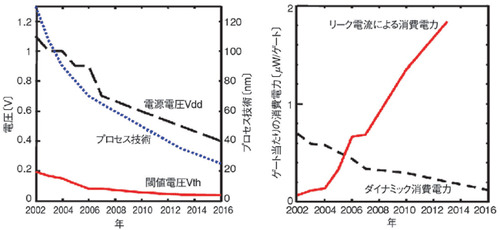

米Synopsys社のフェローであるMike Keating氏は、「プロセス技術を次の世代に移行させることによって微細化を進めるが、電源電圧(Vdd)は低下させなかったとする。その場合、次世代の製造プロセスへと移行することで集積度が2倍になるとすると、電力密度も2倍になる。これではチップが高温になってしまう。そこで、消費電力はVdd2に比例するという関係からプロセスの移行に伴ってVddを低下させることで消費電力を削減しているのだ」と説明する。

また、半導体業界ではここ数世代の製造プロセスで電源電圧を低下させるとともに、トランジスタの閾(しきい)値電圧も下げている。これはドレイン‐ソース間電流(出力電流能力)を維持するためであり、電源電圧の低下によって低下した性能を補うために実施されている。しかし、閾値電圧を低下させるに連れ、サブスレッショルドリーク電流が増加するようになった。

加えて、「プロセスの微細化が進むに連れ、ゲート酸化膜は非常に薄くなり、ゲートリーク電流が指数関数的に増加している」とKeating氏は述べる。「65nmプロセスか45nmプロセスぐらいで、ゲートリーク電流ならびにサブッスレショルドリーク電流によるリーク電力と、ダイナミック消費電力は同じくらいの量になる」(同氏)という。

これまでは、プロセスの微細化を進めても、全体的な電力密度は実質的には変わらなかった。しかし、ITRS(International Technology Roadmap for Semiconductors)は2005年、65nmプロセスでは、ダイナミック消費電力の密度は1.43倍に、リーク電力は2.5倍に増加するだろうとする研究報告を発表した。さらに、45nmプロセスでは、ダイナミック消費電力の密度は2倍に、リーク電力は6.5倍に増加するとITRSは予測する。実際には、65nmプロセスを用いた高速動作の回路では、消費電力の半分までもがリーク電力として失われる。45nmのプロセス技術では、LSIの電力の60%がリーク電力として失われると業界では広くいわれている(図1)。「つい最近までは、速さと消費電力といったような単純なトレードオフの関係に基づき、いくつかのオプション的な手法によって電力の問題に対処していた。しかし、そのような解決法は消滅しつつある。電力を削減するために複数の設計技法を用いることはオプションではなく必須だ」とKeating氏は述べる。

図1 プロセス技術の微細化と消費電力の関係 ITRSのロードマップにおけるロジック回路の微細化と電圧/消費電力の関係を示した。左は、プロセスの微細化に伴い電源電圧(Vdd)と閾値電圧(Vth)が低下している様子を表している。右は、年々の微細化によりリーク電流による消費電力が急峻に増加していることを表している。

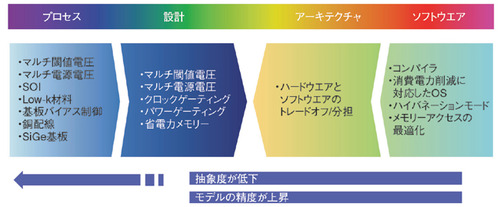

図1 プロセス技術の微細化と消費電力の関係 ITRSのロードマップにおけるロジック回路の微細化と電圧/消費電力の関係を示した。左は、プロセスの微細化に伴い電源電圧(Vdd)と閾値電圧(Vth)が低下している様子を表している。右は、年々の微細化によりリーク電流による消費電力が急峻に増加していることを表している。消費電力増加の問題に対処するために、エレクトロニクス業界ではさまざまな分野において低消費電力化に向けた新しい技法や材料を採用し始めている(図2)。例えば、ファウンドリは、マルチ閾値電圧/マルチ電源電圧、SOI(silicon on insulator)、Low-k材料、基板(ボディ)バイアス、銅配線やSiGe(シリコンゲルマニウム)基板などを導入した。一方、LSIアーキテクチャ設計者やソフトウエアエンジニアは、パワーマネジメント機能に優れたOSを実装/採用したり、ハイバネーションモード(休止モード)をシステム設計に取り入れたりすることによって、ハードウエアとソフトウエアのトレードオフをうまく調整することで消費電力を削減している。また、LSI設計者も回路の消費電力を低減するさまざまな手法を用いている。

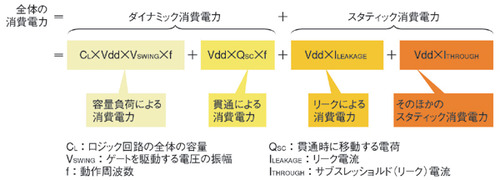

米Sequence Design社のCTO(最高技術責任者)兼バイスプレジデント兼シリコンビジネスユニットゼネラルマネジャのJerry Frenkil氏は、「低消費電力設計とは、『チップの総消費電力=ダイナミック消費電力+リーク電力』という式における右辺の各項の値を小さくすることだ」と説明する。ダイナミック消費電力は、チップ上のゲートやトランジスタが動作する際に消費する電力である(図3)。一方、リーク電力とは、リーク電流によってトランジスタが無駄に消費している電力のことだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

図2 LSIの消費電力を削減するための技術/材料 ファウンドリ、LSIアーキテクチャ設計者、ソフトウエアエンジニア、LSI設計者、EDAベンダーがこぞって消費電力を低減しようと努力している。

図2 LSIの消費電力を削減するための技術/材料 ファウンドリ、LSIアーキテクチャ設計者、ソフトウエアエンジニア、LSI設計者、EDAベンダーがこぞって消費電力を低減しようと努力している。 図3 チップの総消費電力を表す式 低消費電力設計とは、式の右辺にあるダイナミック消費電力、リーク電力を少なくすることである。

図3 チップの総消費電力を表す式 低消費電力設計とは、式の右辺にあるダイナミック消費電力、リーク電力を少なくすることである。