FPGA設計のチェックポイントを知る:ASICからの移行で失敗しないために(5/5 ページ)

検証の問題

FPGAが最初に市場に投入されたとき、その主な特徴として挙げられていたのは、プログラミングが可能で、システムのモデルを実行してボード上で直接テストすることができ、シミュレーションベースのロジック検証を行わずに済むということだった。経験豊かなFPGA設計者の多くが、今でもこの手法を用いる。しかし、Singh氏とRozario氏によると、今日では中規模のFPGAでさえも、単純にプログラミングして、ボード上で動作させ、システムのテストおよび作成中にデバッグするには、大規模で複雑すぎるという。

チップを設計した後、ロジック検証は行わずに、そのチップを実験室でテストしたという話を多くの経験豊かなFPGA設計者らから聞いていたが、Rozario氏はその方法は採用しなかった。なぜなら、同氏のチップにつながるのは標準バスインターフェースであったが、チップ内部は複雑で、チップ内部の状態を見ずにデバッグを行うのは困難だったからである。「波形があるほうがずっとやりやすいため、ASICの検証方法をとることにした」と同氏は語る。「実験室でのデバッグも行ったが、実験室に入る前にほとんどのバグを除去しようと努力した」(同氏)という。

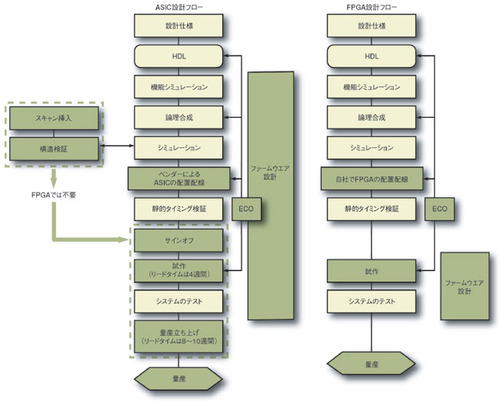

同様にSingh氏の設計グループは最上位のFPGAのみを使用するため、ASICと同じ検証方法をFPGAにも適用し、各回路に対してテストベンチによるシミュレーション、デバッグ、タイミング解析を行うという工程を実行した。「機能シミュレーション、ゲートレベルのシミュレーション、および動的シミュレーションを実行し、ゲートと寄生要素を考慮した上で再び機能シミュレーションを行う。それから複数のコーナーやモードに対し、非常に入念に静的タイミング解析を行った」とSingh氏は述べる。「それによって良い結果が得られれば、基板に載せて電源を入れてみる」(Singh氏)。この方法を初めて実行する際には、数回の繰り返しが必要になるが、「そのうち標準的な作業となり、その後のプロジェクトでは容易に感じられるものになってくる」と同氏はいう。Singh氏の経験上は、この方法が大抵良い結果につながった。FPGAベンダーからは、自社のハード/ソフトブロック、SERDES、PLLなどのマクロに対し、優れたシミュレーションモデルが提供されており、それらが設計グループの検証作業に役立つという。ASICとFPGAの一般的な設計フローを図3に示す。

ソフトエラー

ASIC設計とFPGA設計の間の微妙な相違点に加え、SRAMベースのFPGAには新たな問題もある。それは、ソフトエラーである。ソフトエラーは、空気中に浮遊する中性子がチップに衝突する際に生じ、ビットエラーを起こして、時には誤った信号を生成する*3)。スタンダードセルICでは通常ソフトエラーは生じにくいが、SRAM構造などではソフトエラーが生じやすい。Xilinx社、Altera社、Lattice社などが供給する最上位のFPGAは、SRAMをベースとしたものだ。

Singh氏の設計グループは、ソフトエラーに遭遇する回数が多かったという。そのため同氏は、「チップを選択する際には、信頼性に関する調査結果を求める必要がある」と警告する。「ベンダーがそのFPGAは信頼性が高いと主張したとしても、設計にある程度のECC(error checking and correcting)を加える必要がある」と同氏は語る。SRAMベースのチップには、中性子の衝突によって生じるビットの反転などのエラーが生じないように、ECC構成が必要である。

RAM構成の整合性を検査する制御回路を含む設計を行っていて、時々RAM構成を変更する場合には、ソフトエラーが生じる可能性が高い。ソフトエラーはASIC設計ではあまり生じないが、SRAMベースのロジック構造やオンチップSRAMブロックなど、FPGA上のSRAMベースのセグメントはすべて影響を受ける可能性がある。「トランジスタが小型化し、チップの電源電圧が低くなるに連れ、この影響は避けて通れなくなる。中性子が衝突する危険性が常に伴う」とSingh氏は述べる。

幸いなことに、Actel社やLattice社などのベンダーは、フラッシュメモリーベースのFPGAを提供している。これらのチップはSRAMベースのチップほど高速ではなく高集積度でもないが、ソフトエラーは生じない。また、不揮発性のチップは、違法コピー対策がまだ確立されていない地域を対象とする企業向けに高いセキュリティを提供できるため、人気が高まっている。

ASICを製造するためのマスク代、ASICの開発費、ASIC設計ツールのコストが上昇する中、FPGAベンダーは、設計者が迅速に設計データを実装できるようさまざまな方法を提供している。しかし、FPGAへと移行する前に、FPGAについてよく調査し、各ベンダーのアーキテクチャ、設計ツール、技術サポートを比較する必要がある。また、FPGAの限界を十分に理解し、それに応じて設計手法を補うことも必要であろう。

脚注

※3…『宇宙線によるシングルイベントエラーがLSIを襲う』(Michael Santarini、EDN Japan 2005年10月号、p.85)

Copyright © ITmedia, Inc. All Rights Reserved.