FPGA設計のチェックポイントを知る:ASICからの移行で失敗しないために(3/5 ページ)

FPGA製品の適切な選択

設計者は、さまざまなベンダーからどのようなFPGA製品ファミリが提供されているのかを調べ、性能、消費電力、集積度の面で適切な製品を選択しなければならない。そして、その際には注意すべきことがある。ASICからFPGAへと移行する設計者が最初に知っておかなければならないことの1つは、ある性能レベルを達成するためには、必要と考えるものよりも集積度が20%高い製品を購入すべきだということである。

Singh氏がこれまでに設計した10種のFPGAのほとんどにおいて、FPGAを選択したのは、開発する製品の製造数と性能の要件にそれが適合したからである。「すべてのケースにおいて、動作周波数、I/O数、セル使用率の面で、選択したFPGA製品のスペックの限界値に近いレベルまで使い切ることになった」と同氏は説明する。最初にチップ全体の面積の60〜75%までしか使用せずに設計を行ったのであれば、少しずつ細かい変更を加えることにより性能の要件を満たし、良いテスト結果が得られる可能性が高いという。それに対し、最初の設計でチップ面積の85%以上を使用していると、必要とする性能を達成できない恐れがあると同氏は指摘する。最終的に95%の使用率で目標とする性能を達成できたケースもあったが、それには多大な労力が必要であったという。それには「FPGAとその動作に精通している必要がある」とSingh氏は述べる。ASICの世界では、Tcl(tool command language)で記述したスクリプトを使ってデータベースを検索し、必要な情報を得るといったことが行えるが、FPGAの場合はツールがそれほど発達しておらず同じことは行えない。ほとんどのツールはGUI(graphical user interface)ベースである。

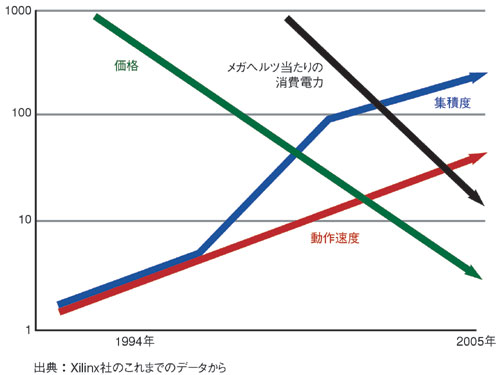

Rozario氏は、初めてFPGAの調査を始めた際、ベンダーがチップの性能や集積度を常に改善しているという事実に感激したという(図2)。Xilinx社によると、市場に存在する最大規模のFPGAで、65nmプロセスで製造されるVirtex-5は、ロジックセル数が33万個で、ASICに換算すれば約1200万ゲートに相当するという。それでもなお、FPGAはASICと同等の最大動作速度や集積度のレベルには達していない。最上位に位置付けられるSRAMベースのFPGAで、機能を抑えて最大動作速度が得られるように最適化しても、せいぜい550MHzである。ASICであれば、最大動作速度でその2倍の性能を達成することができる。

Rozario氏は当初、FPGAの性能の限界を心配していた。しかし、同氏もまたFPGAの動作速度と集積度の進歩に驚かされた。ただし、同氏は「ASICの設計に慣れている場合、FPGAでは性能に関する目標を間違いなく下げざるを得ない」と警告する。同氏によると、最初の設計ではVirtex-5 LX 220の面積のうちの80%を使用することによって、設計プロジェクトの目標性能を達成したという。

今日のFPGAベンダーは通常、複数のバージョンの製品を提供している。1つのFPGA製品ファミリは、基本的なSOG(sea of gates)型のFPGAと、特定の用途/市場に向けてそれを特化したバージョンから構成されるのが普通である。ネットワーク用途をターゲットとし、ハードワイヤードのSERDES(serializer/deserializer)コアを含むものもあれば、通信用途に向けたハードワイヤードのDSPブロックを含むものもある。いずれの製品も、かなり大容量のメモリーを搭載する。例えばXilinx社は、高性能ロジック向けにVirtex-5 LXを、シリアル接続を持つ高性能ロジック向けに「Virtex-5 LXT」を、シリアル接続を持つ高性能DSP向けに「Virtex-5 SXT」を、シリアル接続を持つ組み込み用途向けに「Virtex-5 FXT」をそれぞれ提供している。

Singh氏もRozario氏も、用途に適した製品を選択することが必須だと述べる。FPGA内に、不要なハードワイヤードのコアがあると、それだけチップ面積が大きくなり、設計の後工程において目標性能の達成を妨げるレイアウト上の障害となる恐れがあるからだ。

Singh氏とRozario氏の場合、消費電力が主要な課題となる用途をターゲットとしていたわけではない。しかし、当然のことながら、「低消費電力を目標として設計を行うケースでは、FPGAの消費電力の問題を考慮しなければならない」(Singh氏)だろう。一方で、FPGAベンダーは90nm/65nmのテクノロジノードにおいて、全体的な消費電力とリーク電力を低く抑え込むなど、かなりの進歩を実現していることも事実である。

消費電力の問題に対処するためにSingh氏の設計グループが採用した唯一の方法は、クロックゲーティング技術を用いて、伝送速度が5ギガビット/秒のハードワイヤードのSERDESを使ってないときに停止させるというものである。「新しいFPGAの消費電力はかなり少ない。加えて消費電力を下げるための手法も多く存在する。しかし、われわれはまだそれらすべてを使用しなければならない状況にはなっていない」と同氏は語る。もちろん、サーバー用途のハードウエアも低消費電力をセールスポイントとして強調するような時代になれば、それらの手法を使用しなければならない状況になる可能性はある。

性能とテクノロジノードが同じである場合、一般的にASICの消費電力はFPGAよりもかなり少ない。しかし、この点についてはFPGAベンダーも改良を加えている。Xilinx社とAltera社は、リーク電力の削減に成功し、65nmプロセスを使ったチップのリーク電力が90nmプロセスで製造したチップと変わらなくなったと主張している。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 この10年間に見るFPGAの進化 FPGAは、集積度、消費電力、性能、コストといったすべての面において改善されてきている。

図2 この10年間に見るFPGAの進化 FPGAは、集積度、消費電力、性能、コストといったすべての面において改善されてきている。