PWMコントローラのデューティをクランプ

例えば電流検出トランスや2スイッチ構成のフォワードコンバータなどを利用する電源回路においては、PWMコントローラからの制御信号のデューティサイクルをクランプする機能が必要となる。デューティサイクルにクランプをかけなければ、トランスが飽和してシステムに致命的な故障が発生することになるからだ。ところが、多くの電源回路ではコスト低減のために、デューティサイクルのクランプ機能を持たない低価格なPWMコントローラが使用されている。本稿では、そうしたPWMコントローラを使う場合に、低コストでクランプ機能を付加するための回路を紹介する。

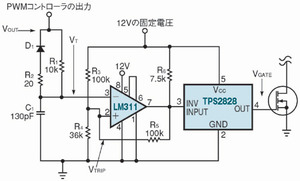

図1の回路は、少数の受動部品、ヒステリシス機能を持った1個のコンパレータ「LM311」とMOS FETドライバICの「TPS2828」で構成される。この回路では、デューティサイクルのクランプ値を抵抗R1とコンデンサC1によって決める。抵抗R2とダイオードD1はPWMコントローラの出力(「UCC28019」であればGATE端子)がローになったときにリセット機能を提供する。抵抗R3、R4、R5はコンパレータの基準レベルVTRIPを5Vに設定する。抵抗R6により、コンパレータは−2.5Vのヒステリシスを持つことになり、回路の安定性が確保される。

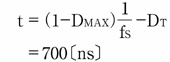

ここでは、デューティサイクルの最大値DMAXを0.9(90%)に設定したい場合を例にとる。PWMコントローラのスイッチング周波数fSは100kHzとしよう。ほとんどのPWMコントローラは100%のデューティサイクルには対応しておらず、一定のデッドタイム(休止期間)DTを持つ。この例の場合、デッドタイムは300nsである。最大デューティサイクルDMAXを0.9にする場合、ドライバ出力をローにすべき時間tは以下の式で求められる。

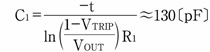

デューティサイクルの設定に用いるコンデンサC1を選択するには、PWMコントローラの出力VOUTの最大値が分からなければならない。この例では、最大出力電圧は12Vとする。このことから、コンデンサC1の値は以下の式で求められる。

このように計算値は130pFになるが、標準品を用いたいので、本稿の例ではC1として120pFのコンデンサを選択することにした。

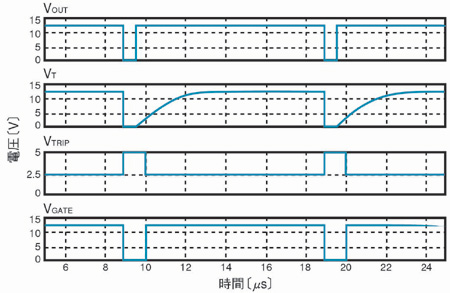

図2に示したのは、図1の回路のSPICEシミュレーション結果である。図において、VOUTはPWMコントローラの出力、VTはコンパレータの反転入力端子の電圧、VTRIPはコンパレータの非反転入力端子の電圧、VGATEはMOS FETドライバICの出力である。図2の波形からドライバ出力VGATEのデューティサイクルが90%になり、クランプ機能が正常に動作していることが確認できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 デューティサイクルのクランプ回路 この簡単な構成の回路により、スイッチングレギュレータのデューティサイクルを90%にクランプできる。

図1 デューティサイクルのクランプ回路 この簡単な構成の回路により、スイッチングレギュレータのデューティサイクルを90%にクランプできる。

図2 図1の回路に対するSPICEシミュレーションの結果 デューティサイクルは90%にクランプされている。

図2 図1の回路に対するSPICEシミュレーションの結果 デューティサイクルは90%にクランプされている。