DDR3がもたらす真のメリット:データ転送速度だけじゃない(1/2 ページ)

DDR技術を用いたDRAMは、パソコンやサーバー機器などのメインメモリーとして広く利用されている。現時点では、DDR2が市場の過半を占めているが、次世代に当たるDDR3への移行も進んでいる。本稿では、DDR3のメモリーインターフェース規格の概要を紹介した上で、そのシグナルインテグリティ性能の高さや消費電力の少なさといった特徴から得られるメリットについて解説する。

この記事は会員限定です。会員登録すると全てご覧いただけます。

DDR2の後継規格

ノート型パソコン、デスクトップ型パソコン、サーバー機器をはじめとする電子機器には、さらなるシステム帯域幅の増大と消費電力の削減が求められている。こうした要求に対応するために、電子機器の業界標準規格は進化を続けている。

JEDEC(Joint Electron Device Engineering Council:半導体技術協会)が策定しているメモリーインターフェース規格であるDDR3 SDRAM (Double-Data-Rate 3 Synchronous DRAM。以下、DDR3)も、その1つだ。DDR3の最新規格JEDEC JESD79-3Aは、最先端のマルチコアプロセッサシステムの要件にも対応している。DDR3は、DDR2の後継規格とされているが、データ転送速度が高められていることはもちろん、動作電圧やロジックなど複数項目の仕様に変更が加えられている(表1)。

DDR2規格は、これまでに求められてきたシステム要件には対応できている。しかし、メモリーに対する要件のレベルはさらに高まっており、一方で半導体技術も進化している。こうしたことから、さらに多くの機能を提供できるよう規格にも進化が求められるのは当然のことだ。

DDR3は、これまでのDDR規格よりも優れた利点をいくつか有している。例えば、1端子当たり最大1600メガビット/秒のデータ転送速度をサポートしながら、動作電圧は1.5Vに抑えられた。この値は、1.8Vで動作するDDR2よりも17%低い。また、DDR3の省電力機能の1つであるパーシャルアレイセルフリフレッシュは、アクティブ状態にないDDR3 SDRAMチップ(以下、DRAMチップ)内の一部のバンクをリフレッシュするというものだが、これは電池で動作するモバイル機器において重要な機能となり得る。さらに、DDR3には、オプションで熱対策(センサー)の仕様が定められている。モバイル機器を設計する技術者は、これを用いて、システムが高性能モードではないときにはリフレッシュサイクルを小さくすることにより、さらに消費電力を節減することができる。

DDR2では内蔵バンク数が4個であったのに対し、DDR3は8個のバンクを内蔵する。これにより、アクセス遅延を最小化した高度なプリフェッチが可能となり、システムの速度をさらに向上させることができる。今後DRAMチップのサイズが大きくなったら、この速度の向上はさらに顕著なものとなるはずだ。

DDR2のI/Oは、1.8Vロジックを採用したJEDEC規格SSTL(Stub Series Terminated Logic)18を使用するのに対し、DDR3は、1.5Vロジックを採用したJEDEC規格SSTL15を使用する。そして、DDR3は、ODT(On Die Termination)、ZQ(Zero Quotient)キャリブレーション、フライバイ(Fly-by)トポロジなどのアーキテクチャを最大限に活用することにより、シグナルインテグリティを改善している。しかし、メモリーのさらなる省電力化に対する要求は非常に高いため、JEDECは現在DDR3L(DDR3 Low Voltage)規格を策定している。

シグナルインテグリティの改善

DDR3の動作は高速であるため、メモリーモジュールを流れる信号のシグナルインテグリティがより重要になる。そのため、DDR3では、シグナルインテグリティの改善を目的とした仕組みがいくつか用意されている。

DDR2モジュール回路のTブランチトポロジに対し、DDR3ではフライバイトポロジが用いられている。このトポロジの違いから、アドレス線と制御線は、DDR2ではモジュールで分岐するのに対し、DDR3では単一のパスによりDRAMチップから別のDRAMチップへと接続される。フライバイトポロジでは、機械的なラインバランシングが不要であり、コントローラがメモリーシステムの補正処理におけるトレーニング中に生成する信号遅延時間を利用する。メモリーモジュール内にあるDDR3対応の各DRAMチップは、キャリブレーションの実行とキャリブレーションデータの保存のための自動レベリング回路を備えている。

また、DDR3では、数種類のインピーダンスキャリブレーションシーケンスを実装することで、シグナルインテグリティを向上するようになっている。電源の投入後にロングZQキャリブレーションを行い、通常動作中に定期的にショートZQキャリブレーションを行って、電圧と温度の影響を補正する。これらのキャリブレーションシーケンスが存在することにより、DRAMチップの出力ドライバとプリント配線板の配線の接続性は大幅に改善される。

DRAMチップのZQ端子は、外部の高精度抵抗に接続される。この外部の高精度抵抗を利用して、出力ドライバのインピーダンスとODTが配線インピーダンスに合わせて調整される。その結果、インピーダンスの不整合が緩和され、信号の反射も抑えられる。また、この高精度抵抗を利用することにより、プロセス、電圧、温度によるばらつきの影響が軽減され、インピーダンス値が適切に制御されて変動幅が小さく維持される。なお、DDR2ではオンチップ抵抗を使用していたので、抵抗値のばらつきにより、十分な調整効果が得られにくい傾向にあった。

DDR3は、高速での信号伝送を改善するためにダイナミックODTを採用している。この回路は、DRAMチップにおけるODTの設定/解除を動的に行うとともに、プルアップ/プルダウン抵抗のネットワークによって適切な値を選択できるようになっている(図1)。これにより、コマンド、アドレス、制御、データ、およびストローブのバスが適切に終端される。また、マザーボード上での静的な終端を採用するDDR2よりも、信号の適切な制御が可能になり、マージンも改善される。

先述したように、DDR3はコマンド/アドレス信号およびクロック信号にフライバイトポロジを採用している(図2)。これにより、シグナルインテグリティの向上が図られている。各信号は、各DRAMチップにリニアに伝送され、最終的にメモリーモジュールのバス終端へと送られる。メモリーモジュール規格の1つに、registered DIMM(Dual Inline Memory Module)がある。この規格では、アドレス、制御、クロックの各信号をバッファするICチップを用いる。これであれば、Tブランチトポロジを用いるDDR2よりもスタブ数とスタブ長を減らすことができる。しかし、DRAMチップにおけるクロックとデータストローブの間に伝播時間(Flight Time)のずれが生じる。この伝播時間のずれは、マザーボードのコントローラ側でレベリング処理を行うことにより、補正することができる。レベリング処理により、DRAMチップは自身のクロックを調整するためのトレーニングシーケンスに入る。

DRAMチップ内部の動作周波数は、DDR2からDDR3に移行しても基本的に変わらない。DDR2では、端子当たりの最大帯域幅は800メガビット/秒となっているが、これを1066メガビット/秒まで拡張することが可能である。DDR2の4ビットプリフェッチに対し、DDR3では8ビットプリフェッチを採用することにより、1600メガビット/秒に達する最大帯域幅が得られるようになっている。

registered DIMMは、高い帯域幅とスループット効率を必要とするシステムに対し、優れた性能を提供するメモリーモジュール規格である。DDR2のregistered DIMMは、少なくとも1個のレジスタICと1個のPLL(位相同期回路)を使用する。DDR3では、レジスタICとPLLを集積したモノリシックICチップを使用する。このICは、プログラマブルドライブ、入力バス終端、出力反転といった機能を持ち、SSO(Simultaneous Switching Output:同時スイッチング出力)ノイズを効果的に低減する。

また、同ICは、消費電力を低減するために、出力反転、出力フロート、入力ロジックの状態を用いたDRAMチップの電源停止といった機能も備えている。加えて、出力ドライバのインピーダンスをプログラミング可能にすることによっても省電力化を図っている。高度な終端手法とインピーダンス整合手法は、集積チップを用いたデータ転送におけるシグナルインテグリティを飛躍的に改善する。このことが、タイミングバジェット(制約)のマージンの増加にもつながっている。

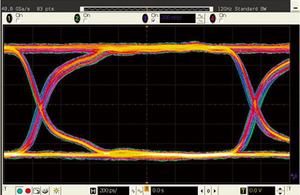

適切な終端値、ドライバインピーダンス、出力反転を適用することにより、ポストレジスタのアイパターンは大きく開き、リングバックは最小となる(画面1)。ビットエラーを防ぐために十分なセットアップ/ホールド時間がコントローラから与えられれば、プリレジスタでも同等の品質のアイパターンが得られる。レジスタIC/PLLを集積したICチップは、ODTを採用していることから、システムを再設計したり大幅な変更を加えたりすることなく、高いスループット効率と速度を実現できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- フェライト(3) ―― 電子部品としてのフェライト

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- アルミ電解コンデンサー(1)―― 原理と構造

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト