大きな入力容量に対応可能なゲート駆動回路:Design Ideas

パワーエレクトロニクスで用いるゲート駆動回路は、コントローラ回路が発生したパルスを、MOSFETやIGBT(絶縁ゲート型バイポーラトランジスタ)などのパワートランジスタに伝達する役割を果たす。ゲート駆動回路には、次の2つの事柄が求められる。1つは、ガルバニック絶縁性を保ちながら、コントローラ回路からの制御信号を伝達し、パワートランジスタをオン/オフさせるためのエネルギーを供給すること。もう1つは、必要な時間だけ、パワートランジスタをオンまたはオフの状態を維持することである。そして、必要なエネルギー量は、パワートランジスタの入力容量が大きくなるに連れて増大する。

一般に、大電力の供給が要求される場合、設計者は複数のパワートランジスタを並列に使用する。それにより、パワートランジスタ全体の入力容量が増加することになる。例えば、IGBTを並列動作させる場合、それぞれのIGBTに対して異なるゲート駆動回路を使用すると、オン時間とオフ時間の変動が大きくなり、各IGBT間の動作に不均衡が生じる可能性がある。そのため、このような場合は、複数のIGBTで1つのゲート駆動回路を共用するべきだ。

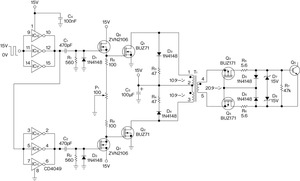

本稿で紹介するのは、入力容量が大きいパワートランジスタに対応可能なゲート駆動回路である。図1の回路を使えば、5nF以上の入力容量を持つMOSFET/IGBT(図の右端のQ5)を駆動することができる。完全なガルバニック絶縁に対応しており、フローティング電源を使う必要がない。また、100%に近いデューティ比の実現も可能だ。

この回路は、筆者らが以前このコーナーで紹介した回路を改変したものであり、元の回路に対してトランジスタQ6とQ7(いずれも「ZVN2106」)を追加したものとなっている*1)。基本的な動作は元の回路と同様だが、トランジスタQ1、Q2、Q3およびQ4としては、それぞれが駆動することになるトランジスタに対応してより大きな電流を扱えるよう、従来のものよりも大電力に対応可能なタイプのものを使用している。具体的には、Q1とQ2には「BUZ71」、Q3とQ4には「BUZ171」を採用した。コンデンサC1と抵抗R1、コンデンサC2と抵抗R2で構成される微分回路は、それぞれ幅が1μsのパルスを発生する。このパルスは、Q1とQ2のゲートに直接入力してはならないが、Q6とQ7のゲートには直接入力してもかまわない。Q1/Q2の入力容量は約700pFと大きな値だが、Q6/Q7の入力容量は約75pFであり、幅の狭いパルスでも正しく伝達することができる。

以下、トランジスタQ7側の経路を例にとり、この回路の動作を簡単に説明する。Q7は、コントロール回路からの制御信号の立ち上がりエッジから1μsの期間にオンになる。それにより、Q7に電流が流れ、Q2の入力容量に対する充電が始まる。Q7のオン抵抗は数Ω(標準値で2Ω)しかないので、Q2の入力容量の充電プロセスは、入力容量の値が大きいのにもかかわらず十分に速い。

充電が進むとQ2のゲート電圧は上昇するが、Q7はゲート−ソース間電圧が低下してオフになる。その結果、微分回路が生成した幅の狭いパルスがQ7とQ2を伝達し、さらにはトランスT1を介してQ3に伝達されることになる。それにより、トランジスタQ5のゲート−ソース間容量が充電される。

トランジスタQ6の経路でも、同様のプロセスにより、Q5の放電動作が実現される。すなわち、駆動用の制御信号の降下エッジの期間にQ6、Q1およびQ4が動作することにより、Q5のゲート−ソース間容量の放電が行われる。

以上のような動作により、パワートランジスタQ5を駆動することができる。

また、この回路では、ポテンショメータP1を使ってQ1とQ2の入力容量の放電時間を制御することにより、パワートランジスタQ5に加える駆動信号のオフセット値を調整可能となっている。上述したように、Q6/Q1およびQ7/Q2は幅の狭いパルスを伝達する。そのパルスの立ち上がり/降下エッジは急峻である。そのため、スイッチング周波数が高い場合であっても、デューティ比を大きく変化させることができる。例えば、スイッチング周波数が20kHzの場合、デューティ比を2%から98%まで調整可能だ。さらに、この回路はそのコンパクトな設計により、パワートランジスタQ5の近傍に実装することができる。結果として、寄生要素を最小限に抑えることも可能である。

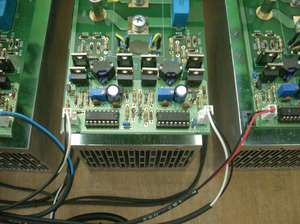

写真1に、10kW/20kHzの3相パワーインバータ用に試作したゲート駆動回路を示した。この回路では、パワートランジスタとしてドイツSemikron International社の「SKM75GB128」を使用している。このトランジスタの入力容量は、実測値で15nF以上ある。この条件において、このゲート駆動回路の消費電流は30mA以下となった。

脚注

※1…Espi, Jose M, Rafael Garcia-Gil, and Jaime Castello, "Isolated FET pulse driver reduces size and power consumption," EDN, March 30, 2006, p.98

Copyright © ITmedia, Inc. All Rights Reserved.