水晶発振器の基本:「水晶発振器」活用の手引き(2)

前回は水晶発振器の基本となる水晶振動子と発振回路の基本について解説した。今回からは、本題である水晶発振器について解説を進めることにする。まず最初に、水晶発振器の種類と基本的な内部構造について説明する。その上で、実際の設計に水晶発振器を適用するために理解しておくべき、各種特性項目について解説する。

水晶発振器の種類

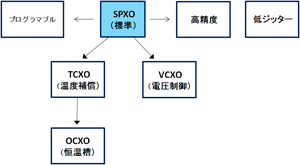

今回は、まず水晶発振器(水晶振動子と発振回路を1つのパッケージにまとめて製品化したもの)の種類から説明を始める。図5に、水晶発振器の一般的な分類方法を示した。供給メーカーによって多少分類の仕方や呼称に違いはあるが、基本的な機能は同様である。以下、それぞれについて簡単に説明する。

■SPXO

SPXO(Simple Packaged Crystal Oscillator)は、水晶発振器の代表的なモデルである。その機能は単純で、電源電圧を印加することにより、所定の発振周波数のクロックが出力される。発振周波数については、数十kHzオーダーから100MHz程度まで広い範囲で製品が用意されている。

■プログラマブル品

通常、SPXOは固定周波数の単一クロック出力に対応するが、中にはユーザーがクロック周波数を規定の範囲内で選択できるようになっているものがある。この種の製品はプログラマブル(Programmable)品と呼ばれる。内部の水晶発振出力を分周し、その分周比を変えることで周波数を選択可能にするものや、PLL機能を組み合わせて周波数を選択可能にするものがある。後者の場合、そのジッター特性はPLLの性能に依存する。

■高精度品、低ジッター品

発振周波数の精度(誤差)や安定性が高いものが高精度(High Accuracy)品として用意されている。また、特定の通信分野用途向けに、特に小さいジッター特性を規定しているものが低ジッター(Low Jitter)品として区分されている。

■VCXO

VCXO(Voltage Controlled Crystal Oscillator)は、電圧制御により周波数を変更可能な水晶発振回路を用いたものである。発振周波数の所定の初期値に対して、規定の入力電圧で制御することにより、規定の範囲内で周波数を変更することができる。通常はシステムのPLLループ内で使用される。

■TCXO

TCXO(Temperature Compensated Crystal Oscillator)は、SPXOに温度補償機能を付加したものである。温度補償が発振回路のループ内で行われる直接型と、発振回路の外部で行われる間接型が存在する。いずれも、温度センサー(サーミスタなど)を組み合わせることで温度補償が実施される。

■OCXO

OCXO(Oven Controlled Crystal Oscillator)は、発振周波数を外部の温度にかかわらず安定に保つために、水晶振動子と発振回路を比較的高温の恒温槽内に収容したものである。このジャンルの製品では、温度補償の性能を向上させることを目的とし、水晶振動子のカット方法の主流がATカットからSCカット(Stress Compensation-Cut)へと移行しつつある。

水晶発振器の構造

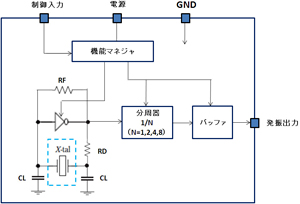

続いて、水晶発振器の構造について説明する。図6に示したのは、水晶発振器(SPXO)の代表的な回路ブロック図である。水晶振動子と発振回路、動作制御回路(分周器、バッファ、機能マネジャなど)で構成されていることがわかる。シンプルな構成のものは、出力のオン/オフを実現する機能マネジャや分周器などは省略され、単純に水晶発振回路とバッファ出力だけとなる。

水晶発振器では、水晶振動子以外のブロックはCMOSロジック回路で実現されている。また、水晶発振回路部の抵抗とコンデンサもCMOSプロセスで製造される(いずれもポリシリコンを使う)。従って、動作電圧、消費電力、出力レベルなどの主要な特性は、CMOSロジック回路の特性(高速のCMOS、低電圧動作のCMOSなど)で決定されることになる。

前回説明したとおり、発振回路に用いるインバータとしては、発振の確実性を得るために、1段構成のものが用いられる。HCシリーズで言えば、「HCU04」タイプ(CMOSの1段アンプ構成)のものが用いられ、「HC04」タイプ(CMOSの3段アンプ構成)のものは使わない。一般的なCMOSの閾(しきい)値レベルは電源電圧Vccの1/2であり、出力クロックのデューティサイクル特性もこの閾値特性に依存する。ただし、水晶発振回路では、発振開始の確実性と安定性、ノイズ対策を考慮して、CMOSのnチャンネル/pチャンネル比をわずかにセンター(1/2Vcc)からシフトさせて用いることもある。

水晶発振器の特性、仕様

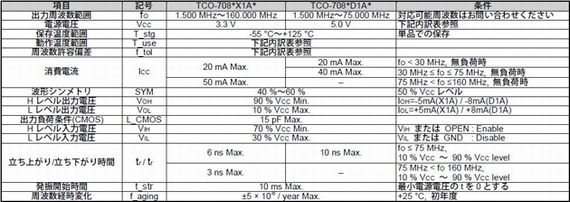

続いて、水晶発振器の特性(仕様)項目とその定義についてSPXOを中心に解説する。図7に、エプソントヨコムのSPXO製品「TCO-708xシリーズ」のデータシートからの抜粋を示しておく。以下に示す各特性項目について記載されているので、これと照らしながら本稿を読み進めれば理解が早いであろう。

実際の設計においては、発振周波数、電源電圧の条件、出力ロジックレベルが最低限必要な仕様となる。ただし、水晶発振器をシステム内に組み込む際には、ほかにも検証を要する特性項目がある。

■公称周波数と周波数許容偏差

公称周波数とは、言うまでもなく、水晶発振器の発振周波数のことだ。ただし、実際の製品のデータシートでは、特定の製品の特定の周波数が規定されている場合と、製品シリーズとして対応可能な周波数範囲(出力周波数範囲)が示されている場合があるので注意を要する。

周波数許容偏差は、実際の製品における公称周波数からの誤差範囲をppm単位で規定したものである。電源電圧、周囲温度、負荷の各条件を含めた誤差範囲が規定されている。例えば、温度範囲A:−25℃〜70℃において±50ppm、温度範囲B:−40℃〜85℃において±100ppmといった具合だ。また、同一製品シリーズにおいて、製品名末尾のサフィックスで許容範囲をグレード分けしているものもある。例えば、製品名A:±100ppm、製品名B:±50ppmのような形である。

周波数許容偏差については、アプリケーションによって要求レベルが異なる。大別すると次のようになる。

- ノート型パソコンなどでの動作クロック:±100ppm〜±200ppm(汎用品)

- デジタルカメラ、FAXなどの動作クロック:±20ppm〜±50ppmm(やや高精度)

- ギガビットイーサーネットに対応した通信機器での動作クロック:±2.5ppm(高精度)

公称周波数を間違えるということはあり得ないだろうが、許容偏差についてはいくつかの条件が設定されているので、それぞれの条件について確認し、実際に設計するシステムに適用できるか否かを検証しなければならない。

■動作温度範囲

水晶発振器が、規定の周波数偏差と出力レベルを満足した状態で動作可能な周囲温度についての規定である。この仕様についても、同一製品シリーズでも温度範囲の規定が異なるものがある。

■電源電圧

水晶発振器の動作電源電圧について、定格電圧(動作電源電圧の標準値)とその許容範囲が規定されている。動作電源電圧は5V系、3.3V系、1.8V系に大別され、通常は、定格電圧に対して±10%の電源電圧範囲を許容している。この仕様は水晶発振器内で用いられているロジック回路の特性と、水晶発振回路の発振条件に依存するものと推測できる。実使用時の電源電圧がデータシートに記されている許容範囲を多少超えても、水晶発振器の動作が急に停止することはない。だが、使用方法としては誤っているので、許容電圧範囲を守って使用しなければならない。

■消費電流

消費電流は規定の電圧を印加して動作させた際、電源端子に流れる電源電流についての規定である。一般的には、発振周波数が高くなるほど消費電流も増加する傾向がある。消費電流の規定は、発振動作の状態が条件となっていることはもちろんなのだが、無負荷の条件で規定しているものがほとんどである。消費電流は標準値(typ)と最大値(max)が規定されるが、実際のアプリケーションでは負荷条件によって消費電流が増加するので、システムの設計時にはこの点について検証する必要がある。

また、スタンバイ(スリープ)機能や、出力オフ(ディセーブル)機能などのモードを有する製品では、それぞれの動作モードにおける消費電流も規定している。

■出力レベル

出力レベルは、水晶発振器からの出力クロックのロジックレベルについて規定したものである。ハイレベルの電圧VOH、ローレベルの電圧VOLについて記されている。具体的には、一般的なロジックレベル、すなわちTTLまたはCMOSに準拠する値でハイ/ローレベルの電圧値が規定されている。例えば、CMOSではハイレベルは電源電圧の90%、ローレベルは電源電圧の10%といった具合だ。

■デューティサイクル/波形シンメトリ

これは、一般的なロジッククロックに適用されるデューティサイクルと同一の定義である。水晶発振器では、内部のロジックデバイスの特性に依存してデューティが決まる。50%のデューティが代表的な値だが、規格としては通常、40%〜60%、あるいは45%〜55%といった値が示されている。

■立ち上がり/立ち下がり時間

出力クロック波形の立ち上がり時間と立ち下がり時間の規定である。ハイレベル/ローレベルの条件は、出力レベルと同様に、TTL/CMOSのものに準拠する。

■出力負荷条件

水晶発振器のクロック出力に接続できる負荷の条件を規定している。負荷抵抗の値(Ω)、負荷容量の値(pF)、ファンアウト(接続できるTTLロジック数)のいずれかが示される。出力クロックの波形は、負荷に対する依存性が比較的大きいので、実際のアプリケーションでの既存の負荷条件と、実装パターンなどによる負荷条件の両方についての検証が必要となる。

■発振開始時間

電源を投入し、水晶発振器の電源が規定の電圧に達してから、実際に安定したクロックが出力されるまでの時間が規定されている。通常、安定したクロックが出力されるまでに、数ms程度の時間を必要とする。データシートでは、電源を供給する際の電圧遷移の条件は規定されていないが、一般的な遷移の範囲であれば問題はないと言える。また、水晶発振器の出力はロジック出力なので、発振が確定するまでの間はハイまたはローレベルのいずれかになる。この点についても、実際のアプリケーションでは、クロックマネジメントの観点からは重要な要素なので、十分な検証が必要である。

水晶発振器の周波数に関する特性は、内部の水晶振動子の特性でほぼ決まると理解してかまわない。また、電源電圧、消費電流、出力に関する各特性は、内部で用いられているロジック回路の特性がそのまま適用されているものが多いと言える。従って、クロックインターフェースについては、一般的なロジック回路の仕様を適用可能である。水晶発振器では、公称周波数と許容周波数範囲、温度特性が重要な仕様となる。

Copyright © ITmedia, Inc. All Rights Reserved.