Xilinx社の最新FPGAは従来比で消費電力を半減、Altera社製品との比較結果も公開

米Xilinx社は2011年6月、東京都内で記者会見を開き、28nmプロセスを用いたFPGAの最新製品「Xilinx 7シリーズ(以下、7シリーズ)」の消費電力に関する報告を行った。

7シリーズには、ハイエンドの「Virtex-7」、ミドルレンジの「Kintex-7」、普及価格帯の「Artix-7」の3つのファミリがある。Xilinx社でアプリケーション&テクニカルマーケティング担当のシニアディレクタを務めるRina Raman氏(写真1)は、「7シリーズを開発する上で、3つのファミリに共通する最優先事項となったのが消費電力の低減だ。具体的には、前世代品である『Virtex-6』や『Spartan-6』と比べて消費電力を半減することを目標とした。今回、この目標値が実現できていることを、実際のハードウエアを用いたベンチマーク結果によって確認することができた」と語る。

このベンチマークは、2011年3月に出荷を開始したKintex-7と前世代品のVirtex-6について、同じリファレンスデザインの評価ボードを用いて行われた。ベンチマークの結果によると、待機時の消費電力は、Kintex-7が0.9W、Virtex-6が3.6Wだった。一方、動作時の消費電力は、Kintex-7が3.1W、Virtex-6が6.5Wだった。これらの事実から、待機時、動作時ともに、Kintex-7の消費電力は、Virtex-6の半分以下になっていることがわかる。

さらに、Xilinx社が強調するのが、この実際のハードウエアを用いたベンチマーク結果と、同社のFPGAの消費電力シミュレータ「XPower Estimator(以下、XPE)」の最新バージョン(version 13.1.1)を用いたシミュレーション結果がほぼ同じだったことである。同社は、「7シリーズの消費電力を正確に評価できるXPEの最新バージョンを投入したことで、顧客による7シリーズを用いた機器開発の後押しが可能になったと考えている。当社と同様に、28nmプロセスを用いたFPGAを開発している米Altera社の消費電力シミュレータは、同社の28nmプロセス製品にはまだ対応していない。こういったツール対応の面で、当社はAltera社をリードできていると考えている」という。

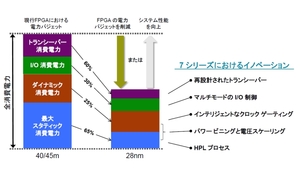

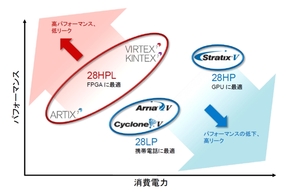

Raman氏は、7シリーズが消費電力を低減できた理由を5つ挙げている(図1)。1つ目は、28nmの製造プロセスとして、台湾TSMC(Taiwan Semiconductor Manufacturing Company)社の「28HPL」を採用したことである。28HPLは、高誘電率の絶縁膜と金属ゲート電極(HKMG:High-k/Metal Gate)を用いた低消費電力版プロセスである。TSMC社は、ほかの28nmプロセスとして、HKMGを用いた高性能版の「28HP」と、ゲート絶縁膜にシリコン酸窒化膜(SiON)を用いた低消費電力を特徴とする「28LP」を展開している。「7シリーズが採用した28HPLは、FPGAに最適なプロセスだ。一方、28HPはグラフィックスプロセッサに最適で、28LPは携帯電話機向けのSoC(System on Chip)などに適している。Altera社は、28nmプロセスのFPGAのうち、ハイエンドの『Stratix-V』に28HPを、ミドルレンジの『Arria-V』と普及価格帯の『Cyclone-V』に28LPを用いている。これに対して、FPGAに最適な28HPLを用いている7シリーズは、製造プロセスのレベルから、Altera社の28nm製品よりも消費電力の面で優位な状態にある」(Raman氏)という(図2)。

2つ目は、パワービニングと電圧スケーリングの採用である。パワービニングとは、半導体のテスト段階で、処理能力が高く、リーク電流の少ないものを選別することである。Xilinx社は、パワービニングを行った品種を「2LEグレード」として販売する方針だ。また、この2LEグレードは、通常の7シリーズの内部電源電圧が1Vであるところを、電圧スケーリングによって0.9Vに下げることが可能である。

3つ目として挙げられるのが、クロックゲーティングを動的に行う機能だ。同機能は、動作時の消費電力の係数となるスイッチング率を、FPGAの動作状況に応じて自動的に調節することができるというものである。これにより、ロジック回路部の動作時消費電力は、同機能を用いない場合と比べて、最大で30%、平均で18%低減することが可能である。また、ブロックRAMについても、動的なクロックゲーティングによりメモリーの動作を最適化することによって消費電力の低減を実現している。同機能を用いない場合と比べて、最大で70%、平均で30%、消費電力を低減できるとしている。

4つ目は、マルチモードのI/O制御機能である。同機能を用いることにより、メモリーの書き込み時やメモリーのアイドル時の消費電力を大幅に削減することができる。そして、5つ目となるのが、新たに設計したトランシーバ回路の採用である。7シリーズのトランシーバ回路は、従来品のものと比べて、消費電力を60%以上低減できているという。

Raman氏は、会見の後半に、7シリーズとAltera社の28nm製品について、さまざまなアプリケーションにおける消費電力の比較結果を示した(表1)。これらは両社の消費電力シミュレータによって算出したものだが、この比較結果が正しければ、7シリーズは、Altera社の28nm製品と比べて大幅な消費電力の低減を実現できていることになる。

なお、7シリーズのシミュレーションには、XPEの最新バージョンを用いている。Altera社の28nm製品については、同社の「Early Power Estimator」(version 11.0 B41)を使用した。Early Power Estimatorは、現時点ではAltera社の28nm製品に対応していない。このため、消費電力の計算では、従来品のパラメータを28nmプロセスに合わせ込んだものを用いている。

(朴 尚洙)

Copyright © ITmedia, Inc. All Rights Reserved.