FPGAの可能性を広げるプロセッサコア(前編):主要プロダクトと実装時の課題を解説!(2/2 ページ)

各社の主要プロダクト

ここからは、主要なFPGAベンダーが提供しているプロセッサコアの概要を紹介していこう。

■Altera

Alteraでソフトウエア/組み込み/DSPマーケティング担当のシニアディレクタを務めるChris Balough氏は、「Niosは、われわれが出荷するデバイスの約30%に搭載されている。Niosのユーザーによって、このアーキテクチャはさまざまな分野で利用できるように拡張されてきた」と述べる。Niosの実績を考えれば、同氏の言葉はやや控えめであるといってよいだろう。

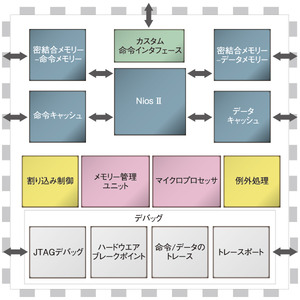

Alteraの組み込み製品マーケティングマネージャを務めるNirmal Kari氏は、「多くの場合、ユーザーはNiosをシステムコントローラとして使用する。また、マルチプロセッサのクラスタ内で、コプロセッサあるいはDSPコアとして使用するのもよくある応用例である。さらには、Niosを使用してステートマシンを実装するユーザーもいる」と述べる。Niosが広範囲にわたる用途で利用されていることから、その機能をサポートするためのハードウエアブロックやプロセッサコアを実装するためのデバッグ回路が多数開発されている(図1)。現在では、カスタム命令ジェネレータ、メモリーマネージャ、Linux用ポートとして、廉価版や高速版のNiosが提供されている。

ユーザーがFPGAにプロセッサコアを組み込む理由はさまざまだ。総所有コスト(TCO:Total Cost of Ownership)についての複雑な分析を行った結果、それがコスト削減につながることが判明する場合もある。FPGAと外部プロセッサの間のインタフェースとなるピンアウトがないなど、技術的な理由による場合もある。また、タスクを変更する可能性がある場合やソフトコアとして実装できる程度に動作が低速な場合、あるいはFPGAの回路に空きがある場合などは、プロセッサコアの配置を決定する明白な理由になるだろう。

■Xilinx

XilinxのMicroBlazeも似たような経路をたどって進化したが、おそらく重視している部分が異なる。同社のプロセッシング製品担当バイスプレジデントを務めるVidya Rajagopalan氏は、「MicroBlazeは主にステートマシンの実装に使用されている。皮肉なことに、FPGAの規模が大きいほど、小規模のプロセッサコアが利用される傾向があるようだ」と述べている。

だが、この傾向によってMicroBlazeの機能拡張が止められることはなかった。Xilinxの組み込みプラットフォームマーケティング担当マネージャを務めるNavanee Sundaramoorthy氏によると、MicroBlazeには、ユーザーが必須としているLinuxポートに加えて、メモリー管理ユニット、メモリー保護機能、単精度の浮動小数点処理機能などが含まれているという。

これは、Xilinxが、ARMのアプリケーション処理用プロセッサコア「Cortex-A9」とFPGAのアーキテクチャを融合させた「EPP(Extensible Processing Platform)」の取り組みに力を入れていることの表れかもしれない(関連記事1)。同社は、EPPを「FPGAにおけるアプリケーション処理への適切なアプローチ」と位置付けている。これに対して、ファブリック内のほかのブロックのシーケンシングや制御といった、組み込み機器としてより下の階層まで連携するような用途ではMicroBlazeを活用していく方針である。ちなみに、Alteraは、同社が今後提供する予定のハードコア製品に関する情報を完全には公開していない。現時点でも、Linuxベースのアプリケーション処理からステートマシンまで、広い範囲に利用できるプロダクトとしてNiosを位置付けている。

■Microsemi

中堅FPGAベンダーのActelを買収したMicrosemiは、同社のシニア製品開発マネージャを務めるTim Morin氏によると、「ARMのマイコン向けプロセッサコア『Cortex-M3』を用いた『SmartFusion』の開発に注力している」という(関連記事2)。なお、同社のミックスドシグナルFPGA「Fusion」では、ARMのFPGA向けソフトコア「Cortex-M1」や、Intelの8ビットプロセッサコア「8051」を搭載できるようになっている。

■Lattice Semiconductor

Lattice Semiconductorは、これまで紹介した3社とは異なるアプローチをとっている。同社のソフトコア「LatticeMico32」は、ほかのプロプライエタリなものとは異なり、オープンソースのIP(Intellectual Property)ブロックとなっている。プロセッサの構造的には、回路規模が小さい最新型の32ビットプロセッサコアと似ており、キャッシュメモリーと高速ローカルRAMの両方にデータを供給する5段のパイプラインや、相互接続機能、周辺IPを備えている。

IPをオープンソース化するという決断は、Latticeが注力するミッドレンジFPGA市場の動向と深い相関がある。同社のソフトウエア製品計画マネージャを務めるMike Kendrick氏は、「LatticeMicoのほとんどのユーザーが次の2つのグループのどちらかに分類される。1つは、外付けのプロセッサへの接続やユーザーインタフェースのホスティングなど、複雑ではあるが高い性能を必要としない機能の実装にこのコアを使用するグループである。もう1つは、システムの起動、消費電力/性能/安全性のモニタリング、デバッグといったシステム管理にこのコアを使用するグループだ。これらのアプリケーションはいずれも、高い処理速度や最新のリアルタイムOS、優れた数値演算能力を必要としない」と説明する。

こういった状況を考えると、オープンソース化のメリットは、ユーザーの利便性の向上以外にも意味が出てくる。先に述べたように、LatticeMicoは、高い処理性能が必要とされない。しかし、オープンソースなので、ユーザーはすべてのRTL(レジスタ転送レベル)にアクセス可能だし、容易に理解できるシンプルな回路設計を維持することもできる。もちろん、RTLにアクセス可能ということは、RTLソースを参照し、内容を見て、変更することができることを意味する。

* * *

後編では、インターコネクト、メモリー、アクセラレータ、デバッグという4つの観点から、FPGAにプロセッサコアを実装する上での課題を説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング