ポータブルがん検出器に見る回路設計の指針:NMR分光の応用で低コスト化に成功(2/4 ページ)

電子回路に必要なパラメータ

ここまで、がん検出器のセンサー部に当たるNMR分光について説明してきた。しかし、筆者が担当したのは、NMR分光を行うための電子回路基板の設計である。そこで重要になるパラメータはラーモア周波数である。

NMR分光分析装置に使用されているラーモア周波数の大半は10M〜100MHzの間にある。この周波数帯域は、これまでに提案されてきた数多くのRF回路に関する設計の考え方を応用できるので、回路設計を行う上で都合が良い。受信回路の設計は容易な作業ではないが、数千km離れた場所から送信された短波信号を受信/識別する回路を設計するのと比べればたいしたことではない。

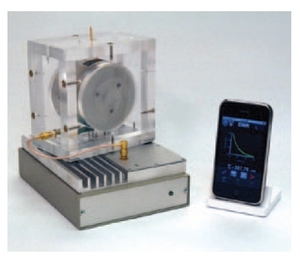

NMR分光の場合、S/N比(信号対雑音比)は基本的に静磁場の大きさに対応して増加する。このため、測定対象に印加する磁場をできるだけ大きく保つ必要がある。つまり、測定対象が大きい場合は、スーパークーリングコイルを備えた大型の超伝導磁石を使用する必要が出てくる。一方、測定対象が小さければ、手のひらサイズの永久磁石であっても1T以上の磁場を印加することができる。今回開発したポータブルがん検出器(正式名称は「DMR-3」)に用いた小型磁石は、測定対象に約0.5Tの磁場を印加することができる(図2)。緩和時間は数msから数sである。復調信号は数十kHzの範囲内で変動するため、約1秒の間に100kHzの周波数でデータを取り込む必要がある。このデータ取り込みを行う回路についても、RF信号の処理回路と同様に実現はそれほど難しくない。

4枚のプリント基板で構成

DMR-3の電子回路は、受信信号を印加するRF信号の周波数で復調し、復調したアナログ信号を数sの間10万サンプル/秒でデジタル信号に変換する必要があった。このサイクルを複数回繰り返した測定結果は、分析のためにホストコンピュータに送られる。すべてのRFパルスの送信タイミングは誤差1μsよりも高い精度が要求された。ホストコンピュータは、USBインタフェースと非同期インタフェースポートを介してすべてのパラメータを制御できるようにしなければならなかった。また、頑丈かつ持ち運び可能な筺体を選ぶ必要もあった。なお、DMR-3が最初に実地で利用される場所はアフリカである。

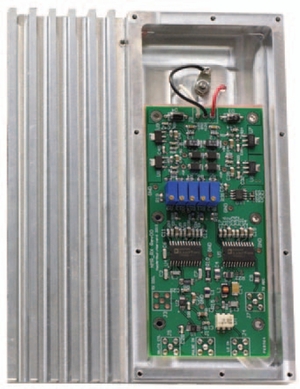

まず、筐体はLansing Instrumentの「MicroPak」を採用した。上部カバーは特注のアルミニウム製ブロックで置き換えている。このブロックは、送信回路を冷却するヒートシンクと受信回路を内蔵するケースという2つの役割を持っている。筺体内部には、筺体の底部に制御ボードとA-Dコンバータボード、アルミニウム製ブロックの裏側にDDS(Direct Digital Synthesizer)ボードが組み込まれている(図3)。一方、アルミニウム製ブロックの中には、受信回路を搭載したボード(RFボード)が内蔵されている(図4)。制御ボードは、Texas Instruments(TI)が「Delfino」ブランドで展開している32ビットマイコン「TMS320F28235」(以下、Delfino)、Integrated Silicon Solution(ISSI)の1Mワード×16ビットのSRAM「IS61WV102416」Future Technology Devices International(FTDI)社のUSBインタフェースIC「FT245」を搭載している。

Delfinoは32ビットの演算処理を高速で実行するほか、高分解能のPWM(パルス幅変調)回路やタイムスタンパ、UART(Universal Asynchronous Receiver/Transmitter)やCAN(Controller Area Network)などの入出力インタフェース、DMA(Direct Memory Access)コントローラなど、開発対象となるがん検出器に必要な周辺回路を備えている。最も重要なのは、Delfinoがランタイムデバッグをハードウエアでサポートしていることだ。ブレークポイントの設定以外にも、プロセッサが最高速度で演算処理を実行している最中にメモリやレジスタ領域の確認、変更、記録が可能である。

回路設計の構想段階で検討したFPGAについては、高価なこともあって採用しなかった。十分に機能を果たしている25米ドルのマイコンを、250米ドルもするFPGAに置き換えることが正しい選択とは思えない。また、FPGAで一般的なBGAパッケージを少量生産の機器に用いるのは問題がある。何より、FPGAを採用するに当たっての最大の障壁はソフトウェアだ。筆者が知る全てのベンダーのFPGAについて、新しいIPコアが宣伝された通りに動作しなかったり、バージョンアップ後のソフトウェアがどういうわけか評価ボードの動作を止めたりという事態が発生していることはその証左だ。

とは言うものの、回路設計を誤ったときの対策にもなる上に、リサイクルして他の機器に使用できることもあって、筆者は回路設計を行う際に小型のFPGAやCPLDをいくつか利用することにしている。例えばDMR-3はCPLDを2個搭載している。副次的なメリットとしては、FPGA/CPLDの利用がバスの最適化やボードの不具合解決につながって、プリント基板の層数を6層からより簡素な構造の4層に変更できることもある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング