デジタル制御電源を学ぶ(2) デジタル制御用ICの特徴を理解しよう:Design Hands-on(1/3 ページ)

前回は、「デジタル電源は何がどう『デジタル』なのか」という基本中の基本を押さえた。今回は、次回以降の「実践編」に入る前の準備として、ソフトウェアによるデジタル制御を実現する制御IC(マイコンやデジタルシグナルコントローラ(DSC)、DSP)の特徴について、アナログ制御と対比させながら解説する。

電源制御回路の動作をおさらい

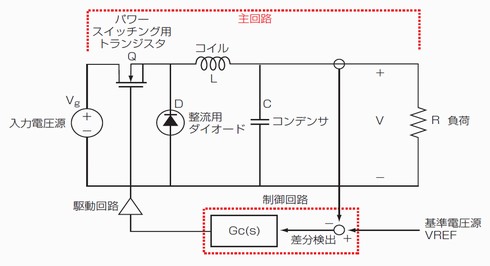

電源制御回路の仕組みを理解するため、まずはその動作をイメージしよう。図1は、前回も紹介したバックコンバータの構成例である。制御回路は主回路から得られる情報を元に、電力をどのように変換するかを判断し、操作量(制御量)を求める機能を受け持つ。

図1中のコイルLに流れる電流は、トランジスタQの時比率(オン状態とオフ状態を切り替えるスイッチング周期に対するオン時間の比率)で表わされる制御量で決まる。制御回路は、コイルLに流れる電流をコンデンサCで平滑した出力電圧Vが所定の電圧に(Vを一定の比率で分圧した電圧が、基準電圧VREFに等しく)なるように、この時比率を制御する。

具体的には、Vが所定の電圧より低ければ、トランジスタQのオン時間が長くなるように制御して時比率を高めて、Vが所定の電圧より高ければQのオン時間が短くなるように制御して時比率を低くする仕組みだ。この制御には通常、PWM(パルス幅変調)を使う。すなわちトランジスタQをオン/オフするゲート駆動信号にPWMを施せば、PWMのパルス幅に比例して時比率を高くしたり低くしたりすることができる。

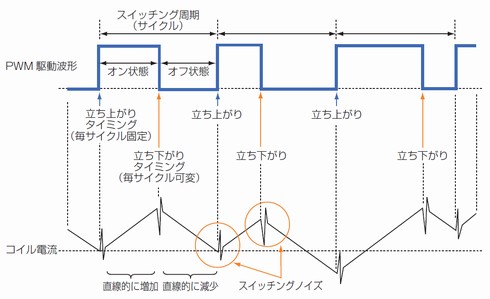

では、トランジスタQの時比率を操作するPWM駆動波形を見てみよう。図2は、スイッチング周期を固定したPWM駆動波形である。これを観察すると、オフ状態からオン状態への立ち上がり遷移はスイッチング周期に同期して周期的に同じタイミングで現れ、オン状態からオフ状態への立ち下り遷移は時比率で定まるタイミングで現れることが読み取れる。つまり、スイッチング電源はこの立ち下りタイミングの変化のみで制御量を操作していることになる。これに着目すれば、制御回路はある立ち下りタイミングと次の立ち下りタイミングの間(およそスイッチング周期に相当する時間)に次の制御量を決定すれば良いことが分かる。

制御量を操作する作業は、大きく分けて3つのステップから成る。まず(1)実際の出力電圧を計測するステップ、次に(2)所定の出力電圧との差分から制御量を求める信号処理のステップ、最後が(3)PWM駆動波形のパルス幅を変化させる制御のステップという流れである。表1では、この3つのステップそれぞれで取り扱う信号の形態の違いに着目し、アナログ制御方式とデジタル制御方式を比較した。

(3)制御のステップでは、アナログ制御もデジタル制御も、PWMの離散時間信号を扱うという点は同じだ。いずれの制御方式を使っても、スイッチング周期毎に計測した出力電圧の情報から次のスイッチング周期の制御量を導出し、立ち下りタイミングまでに制御量を更新すれば良いという点も変わらない。

デジタルPWMの時間分解能に注意

ただし、1点補足を加えておこう。アナログ制御方式では、アナログコンパレータを使ったアナログPWM波形生成器を使うため、PWM波形の実態は連続的な振幅の信号になり、立ち下り遷移を任意のタイミングに配置できる。一方でデジタル制御方式は、デジタルPWM波形生成器を用いるので、PWM波形の実態は離散的な振幅の信号になる。そのため、デジタルPWM波形生成器の最小時間分解能で表現できるタイミングにしか立ち下り遷移を配置できない。これは誤差の要因になる。

ではその誤差の大きさはどの程度だろうか。ここで仮にスイッチング周期が10μs(スイッチング周波数が100kHz)だとすると、最小分解能が1nsのデジタルPWM波形生成器では、遷移タイミングの理想的な位置に対する時間誤差は最大で1ns/10μs=0.01%になる。

ここでもう一度、図2を見てほしい。今度はPWM駆動波形とコイル電流の関係に注目する。コイル電流はPWM駆動波形のオン状態とオフ状態でそれぞれ直線的に増加、減少していく。従って、遷移タイミングの時間誤差は1:1の関係でコイル電流の誤差に変換されてしまうことになる。つまり上記の条件ではコイル電流にも0.01%の誤差が生じるわけだ。もしスイッチング周期が1μs(スイッチング周波数が1MHz)に短くなれば、この誤差は0.1%に増えてしまう。デジタル制御を採用する際には、この誤差が電源回路の許容範囲内に収まることを確かめる必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング