もう一つのコンバータ、フライバック:超入門! イチから覚える電源回路(7)(2/2 ページ)

余談ですが、前ページ図3のFETのドレイン電圧Vdに着目してください。FETのドレイン電圧Vdには電源電圧Edと負荷電圧EBが加算され、FETの電圧定格は少なくともこの値以上が必要であることが分かります。また、FETがOFFするときのオーバシュート電圧、さらにLの電流が0の区間で減衰振動電圧が描かれています。これは結局、回路図にない回路で発生するものです。

例えば、FETの寄生キャパシタンス、Lの巻線間の寄生容量、さらに回路配線のインダクタンスなどによる振動系が構成されていることによるものです。実際の回路の波形観測ではこれらが目立ちますが、性能に寄与するものではなく、EMIなどの発生の要因になります。部品の選択や回路の実装も工夫しなければなりません。

2. 電流連続モード

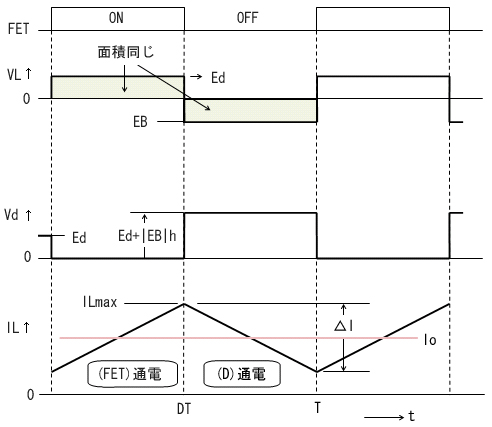

図4に各部の波形を示します。インダクタLの電流は連続して流れるので、Lに発生する電圧はΔIによります。

図4を見て分かるように、Lに発生する電圧はFETのONとOFFとで面積が等しいので、

Ed×DT+EB×(1-D)T=0

∴EB/Ed=−D/(1-D) (6)

この場合は回路の体格に関係なしにデューティDを変えることにより、出力電圧、電流を昇降圧制御できます。

前回と今回でコンバータは入力電源からどのような電流を取り出すのかを見てきました。運転周波数の繰り返しでFETのON時に三角や台形の電流波形を取り出すことが分かったと思います。つまり、大容量のキャパシタを用意すればいいではないかという簡単な話で、これがコンデンサインプット型の整回路が多用されてきた理由の1つです。

次回はこのパルス電流と交流電源の関係について解説したいと思います。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- オン抵抗30%低減 ロームの第5世代SiC MOSFET

- 独自の温度制御技術を搭載 TELの個片化デバイス向けプローバー

- 15G〜20GHz対応のウィルキンソン電力分配/合成器、Vishay

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

図4 各部波形タイムチャート(電流連続)

図4 各部波形タイムチャート(電流連続)