フォトカプラでもラッチ回路ができる!?:Wired, Weird(1/3 ページ)

2端子ラッチ回路というと多くの読者は“サイリスタSCRを使ったラッチ回路”を思い浮かべるだろう。まさにその通りなのだが、少し発想を変えると、サイリスタよりも手ごろなフォトカプラで2端子ラッチ回路が構成できることが分かった。今回は、“フォトカプラのラッチ回路”を紹介しよう!

今までにシリアルオシレータやシリアルタイマーといった2端子の機能回路を紹介してきた。

今回はちょっと風変わりな2端子ラッチ回路が確認できたので報告しよう。

2端子ラッチ回路というと多くの読者は“サイリスタSCRを使ったラッチ回路”を思い浮かべるだろう。まさにその通りなのだが、少し発想を変えると、サイリスタよりも手ごろなフォトカプラで2端子ラッチ回路が構成できることが分かったのだ。

“フォトカプラのラッチ回路”の説明の前に、まずはラッチ回路の構成をおさらいしよう。

そもそも「ラッチ回路」とは

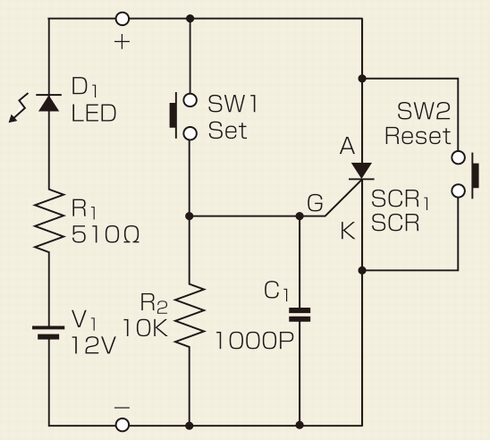

ラッチ回路には、ラッチのセット信号とラッチのリセット信号の2つの信号が必要だ。また電源投入時にラッチが誤動作しないようパワーオンリセットの回路も必要になる。図1にサイリスタSCRを用いた2端子ラッチの回路例を示す。

図1の左側が電源と負荷で、右側が2端子ラッチ回路になる。サイリスタSCRはPNPN素子で、ゲート(G)に0.8V程度の電圧が印加されるとSCRが導通して自己保持するように動作する。

では詳細に回路動作を説明する。SCRのゲートGとカソードKは抵抗R2で接続され、電源投入時にはSCRはオフし、SCRのアノードAには電源電圧の12Vが印加されている。セットスイッチ(SW1)を押すと、ゲートに電圧12Vがかかる。このときSCRは即座にオンして、アノードが約1Vの電圧になり負荷のLEDが点灯し、この状態はラッチされる。つまりセットスイッチ(SW1)をオフしてもSCRのオン状態のままでLEDは点灯する。リセットスイッチ(SW2)を押すとSCRのアノードからカソードへ流れている電流がSW2に流れ、SCRの内部に電流が流れなくなる。このためSCRはオフしてラッチは解除される。この時LEDは点灯のままだが、リセットスイッチをオフにするとLEDが消灯する。

なおサイリスタのゲートをオープンにすると誤動作しやすいので、ゲートとカソード間に10KΩ程度の高めの抵抗と1000pF程度の小さいコンデンサを入れることでラッチ回路の誤動作を防げる。

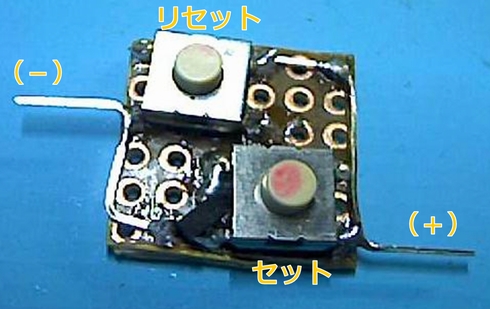

2端子ラッチ回路の製作例の基板の写真を図2に示す。

図2では2個のスイッチしか見えないが、SCRや抵抗の表面実装部品(SMD)を使っては15mm角のサイズでラッチ回路を作った。スイッチを小型化すれば、10mm角サイズでも作れるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

【図1】サイリスタSCRを用いた2端子ラッチの回路例

【図1】サイリスタSCRを用いた2端子ラッチの回路例 【図2】2端子ラッチ回路の製作例

【図2】2端子ラッチ回路の製作例