高速な電圧-電流変換器として動作する回路:Design Ideas アナログ機能回路(1/2 ページ)

電圧-電流変換器や高精度で帯域幅の広い可変利得のカレント・ミラーとして動作する回路を紹介する。高速ICや電流出力型D-Aコンバータの入力を備えたデバイスのテストなどに向けた回路だ。

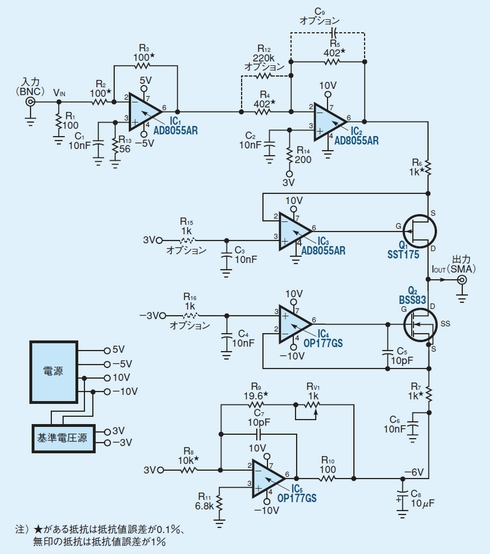

図1の回路は、電圧-電流変換器や高精度で帯域幅の広い可変利得のカレント・ミラーとして動作する。高速ICや電流出力型D-Aコンバータ(以下、DAC)の入力を備えたデバイスのテストなどに向けたものだ。可変電圧源を使ってテストの対象となるデバイスを制御できるようになる。

一般に可変電圧源は容易に入手できるが、可変電流源は入手困難だ。この回路の出力をデバイスの電流入力端子に接続すれば、電圧源だけでテストできる。可変電流源は不要である。従って、テスト回路が簡単になる。さらに、この回路は、入力に直流の可変電圧源を用いることにより、可変利得オペアンプの電流制御を簡単かつ正確に行うことができる。

図1は、電圧-電流変換器として構成した回路である。図に示した抵抗やコンデンサの部品定数を使えば、回路全体の利得は1mA/Vとなる。利得を変更したいときには、部品定数を変えればよい。この回路は、ソース電流とシンク電流のどちらにも対応する。

オペアンプIC1の反転入力は仮想接地であるので、入力VINから抵抗R1と抵抗R2の並列接続により、入力インピーダンス50Ωの信号がIC1に供給される。IC1は、この信号を抵抗R3とR2から求められる利得R3/R2で反転する。

オペアンプIC2はIC1から受信した信号に、抵抗R5と抵抗R4から求められる−R5/R4=−1の利得を与える。さらに、IC2の非反転入力端子は3Vの基準電圧源に接続されている。このため、VINがゼロのとき、IC2の出力電圧と電流検出抵抗R6の上端の電圧は接地に対して6Vのオフセットになる。

電流源の回路は、オペアンプIC3とp型のJFETであるQ1で構成する。バイポーラ・トランジスタではなくJFETを選択したことにより、高速性能や直流誤差、出力電流特性のほぼ完全な直線性を保証している。JFETとしては米Siliconix社の「SST175」を選択した。このJFETは、7mAのドレイン‐ソース間電流IDSSを保証しており、高速で低容量である。

IC3はQ1のソース側電圧であるR6の下端の電圧を3Vにクランプする。従って、信号入力がないときには、Q1は3mAの一定の静止バイアス電流を3mAの定電流シンク回路に流し込む。この電流シンク回路は、オペアンプIC4とn型MOS FETのQ2で構成する。

図1に示した回路全体の出力は、Q1とQ2のドレインから取り出すので、ゼロである。VINが接地よりΔVINだけ高い電圧になると、R6の上端の電圧は同じ量だけ増加する。この結果、R6を流れる電流がΔVIN/R6だけ増加し、増加分が出力電流IOUTになる。R6=1kΩなので、この回路の利得は1mA/Vである。

Copyright © ITmedia, Inc. All Rights Reserved.