高速な電圧-電流変換器として動作する回路:Design Ideas アナログ機能回路(2/2 ページ)

図1の回路は、オペアンプIC3が電流検出抵抗R6の下端を一定電圧にクランプすることで、入力信号によって変化しないようにしている。この点が、図2に示した従来の高精度の電流源回路と異なる。その代わり、通常は固定電圧源に接続されるR6の上端の電圧が、入力信号に応じて変化する。さらに、Q1は常に導通しているので、VINが変化してもQ1のゲート電圧の変化は通常200mV以下である。この結果、VINがゼロから高い電圧方向、または高い電圧からゼロ方向にステップ変化しても、Q1のゲート・チャンネル容量を通して発生する不必要な電流スパイクを出力しない。

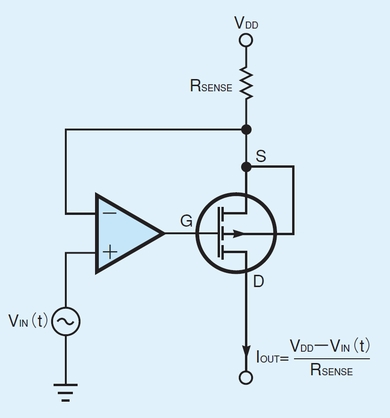

図2の電流源回路は、電流シンク回路を備えていない。このため、出力電流をゼロにするとき、オペアンプはFETを完全にオフにする必要がある。この際、オペアンプの出力は正の電源電圧に近い飽和領域まで数Vも立ち上がるため、大きな振幅の電流スパイクを出力する。さらに、オペアンプが飽和領域から回復し、再びFETをオンするために逆方向に立ち上がるときには、同じ大きさで逆極性の電流スパイクを発生する。

図1に示した3mAの定電流シンク回路は、IC4とQ2で構成する。IC4は電流検出抵抗R7の上端を−3Vにクランプする。基準電圧回路がR7の下端を−6Vに固定しているので、Q2を流れる静止電流は常に3mAで一定である。この静止電流は、VINがゼロのときにQ1を流れる電流に等しい。VINが接地電圧よりもΔVINだけ低くなると、R6の上端の電圧は同じ量だけ低下する。従って、Q1の電流は3mAより小さくなり、その差分の電流ΔVIN/R6が負荷から電流シンク回路に流れ込む。

R7の下端の電位を固定している−6Vの基準電圧回路は、3Vの基準電圧源に公称利得が−2のオペアンプIC5を接続することで実現した。この−6Vの基準電圧回路は、可変抵抗RV1を使って調整する必要がある。例えば、入力信号がないときは、出力電流をゼロに調整する。この際、Q1の静止電流とQ2の静止電流は等しくなる。この1回の調整で信号経路全体を校正できる。すなわち、抵抗値の誤差、オペアンプの直流誤差、±3V基準電圧回路の誤差の影響を打ち消すことができる。しかし、有限の開ループ利得の影響は残る。信号経路の帯域幅を最大化するために、オペアンプには米Analog Devices社の「AD8055AR」を用いた。このオペアンプは、10Vの電源電圧でしか動作しないので、IC1は+5Vと−5Vの2電源が必要である。一方、IC2とIC3は入力電圧が接地より3V高いため、10V単一電源で動作する。

IC4とIC5には「OP177GS」を使い、3Vの基準電圧を取り出す回路には「AD780BR」のような高品質の基準電圧源ICを用いることで、最適な直流電圧精度と安定性が得られる。−3Vの基準電圧源は、3Vの基準電圧源の出力を固定利得−1の回路に通すことで得る。これは、−6Vの基準電圧を得た回路と同様の構成である。

図1中に★の印を付けた抵抗には、誤差が0.1%以下のものを使う必要がある。オプションとして抵抗R12を挿入すると、利得を0.11%高められる。これにより、IC1とIC2で構成される有限の開ループ利得を補償できる。抵抗R15と抵抗R16を追加すると、直流安定性をさらに最適化することが可能である。

しかし、試作品にはこれらの抵抗を使わなかった。100Ωの抵抗負荷を駆動したときの実験では、1VPPの正弦波入力に対して、この回路の帯域幅は80MHzだった。この実験では、オプションのコンデンサC9を使用していない。同じ負荷を使い、1V、2.5nsのステップ波形を入力して500MHzのオシロスコープで観察すると、この回路の出力の立ち上がり時間と降下時間は、それぞれわずか5.5nsと4.8nsだった。しかも、オーバーシュートは観測されなかった。標準出力電圧範囲は−2.8V〜1.7V、ひずみを発生させずに電流を出力できる範囲は−2.1mA〜2.1mAである。

周波数応答性と直線性を最適化するには、この回路を使って仮想接地負荷を駆動すればよい。言い換えれば、電流-電圧変換器回路として帯域幅の広いオペアンプを用いる。この他の負荷を駆動する場合には、常に低いインピーダンスが必要である。また、負荷の一部が容量性のときには、速度は少し低下するが、R5に対して小さな容量のC9を並列に接続して、全体の過渡応答性を最適化したほうがよいようだ。

R1を取り外し、R2と抵抗R13の抵抗値を0Ωに変え、R12の抵抗値を470kΩに増やすと、回路全体の利得が0.1mA/mAの電流-電流変換器になる。例えば、市販されている電流出力型DACのフルスケール出力は、ASICの入力に必要な範囲を超えるのが普通だ。しかし、今回示した回路を使えば、DACの出力電流を調整できる。従って、この回路をASICの入力とDACの出力の間に挿入すれば、電流駆動入力のASICをテストできる。特に、この回路構成では、IC1は利得0.1V/mAの電流‐電圧変換器として動作し、DACの出力に対して仮想接地として働く。すなわち、DACの直線性を最適化する負荷の役割を果たす。

この回路は電流のソ−スにもシンクにもなるので、電流ソース型DACと電流シンク型DACのどちらにも使える。高速に動作させるときには、R3と並列に小さな容量のコンデンサを接続して、DACの出力容量や浮遊容量などの影響を打ち消す必要があるだろう。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

オペアンプ1個で、コモンモードノイズを抑える

オペアンプ1個で、コモンモードノイズを抑える

オペアンプを使って、コモンモードノイズを相殺するアイデアを紹介する。 ADCの入力振幅をプログラマブルに変更

ADCの入力振幅をプログラマブルに変更

マイコンのA-Dコンバータのアナログ入力端子には、マイコンの電源電圧以下の信号しか入力できない。従って、より広い電圧範囲のアナログ信号を扱いたい場合には、外部回路が必要だ。さほど精度を要しない用途の場合には、より簡易的に入力電圧範囲を変更したい。そこで、マイコンの内蔵ポートの出力を切り替えるだけで、入力電圧範囲を0V〜5Vから0V〜20V、−10V〜10Vに切り替える方法を紹介する。 ミキサーを使ってD-A変換器の速度を2倍に

ミキサーを使ってD-A変換器の速度を2倍に

2個のD-A変換器をインターリーブしてシングル・ユニットとして使い、D-A変換器の変換速度を実効的に2倍にする回路を紹介する。 プログラマブル・ロジックを使ったVCO

プログラマブル・ロジックを使ったVCO

可変周波数の発振器を構成する方法として、NORゲートを2個用いたRC発振回路を考案した。この回路による可変周波数範囲は広い。 デューティ比の電圧制御が可能な発振回路

デューティ比の電圧制御が可能な発振回路

本稿では、電圧コンパレータを使って、便利なクロック発生回路を構成する方法を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 従来の電流源回路

図2 従来の電流源回路