容量センサーの低域遮断周波数問題を解く:Design Ideas アナログ機能回路(1/3 ページ)

容量センサーのアナログ周辺回路を設計するときに最初に直面する問題は、低域遮断周波数だ。理論的には、初段のプリアンプの入力インピーダンスを大きくするといい。しかし、簡単に見えるこの設計要求の陰には、数多くの問題が待ち構えている。

低域遮断周波数を解決するには

容量センサーのアナログ周辺回路を設計するときに最初に直面する問題は、低域遮断周波数である。理論的には、1つの簡単な要求を満足すればよい。すなわち、初段のプリアンプの入力インピーダンスを十分に大きくすることである。

しかし、簡単なように見えるこの設計要求の陰に、実際には数多くの問題が待ち構えている。まずプリアンプの能動素子は、ある決まった直流動作点を備えていなければならない。初段の能動素子に電界効果素子(接合型FETやMOSFETなど)を用いれば、直流入力電流を低くできるので、多くの場合は直流動作点を無視できるようになる。

一方で回路には、入力電極に必要な直流電位を与えるために、何らかの直流経路を生じるような抵抗器を取り付けなければならない。例えば高品質の容量式マイクロホンのような、20pF〜50pFという小さな静電容量の小型容量センサーを考えてみよう。この場合、50Hzという高い遮断周波数を得るだけでも、抵抗値は108Ω〜109Ωといったオーダーになる。このような値の抵抗器は、表面実装品では入手しにくい。しかも高価で、精度と安定性が低く、かさばり、雑音が大きい。

外部分極電圧(バイアス電圧)を必要とする場合

さらに難しいのは、容量センサーが外部分極電圧(バイアス電圧)を必要とする場合である。分極電圧は100V以上に達することもある。この分極電圧を別の回路を使ってセンサーに加えなければならない。センサーの少なくとも一端を接地しなければならない場合、これは簡単に実現できないことがある。

プリアンプは、可能な限りセンサーに近づけたい。必要とする空間を最小限にとどめ、接続用リード線の本数を少なくし、発熱をできる限り抑えるべきである。

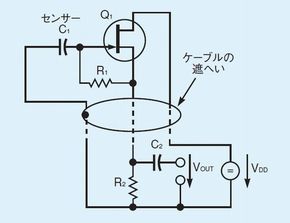

これらの課題に対応した回路の例を図1に示す。接合型FETであるQ1のソース・フォロワ動作による正帰還を利用して、ゲート抵抗R1の値を増倍する。増倍係数αはα=gfsR2である(ここでgfsは、コモン・ソース接続における微分順伝達アドミタンスの実数部分)。代表値としてセンサー容量C1=33pF、適切な値として抵抗R1=10MΩとR2=10kΩ、控えめな値としてgfs=5mA/V(接合型FET「BF245B」のVGS=0V、VDS=15Vにおける代表値)を仮定すると、低域遮断周波数は次式で求められる。

センサー容量C1が極めて小さく、その他の部品の値が控えめであるにもかかわらず、この回路によって相応の遮断周波数を得られる。同時に、センサーの一端を直接接地しながら、センサーに必要な高い分極電圧を得るために、電源電圧としてVDD=VDS+VPOLARIZING=115V を利用できる。ここでVPOLARIZING=IDR2、IDは選択したVDS値(15V)およびVGS=0Vにおける接合型FETのドレイン電流である。従ってセンサーには、100Vの分極電圧を印加できる。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:容量センサーの増幅回路(高いバイアス電圧を必要とする場合)

図1:容量センサーの増幅回路(高いバイアス電圧を必要とする場合)