並列接続IGBTの駆動:ゲート抵抗は共有すべきか否か(2/3 ページ)

» 2016年03月31日 11時30分 公開

[Alan Ball(ON Semiconductor),EDN Japan]

ゲート抵抗の構成オプションをテスト

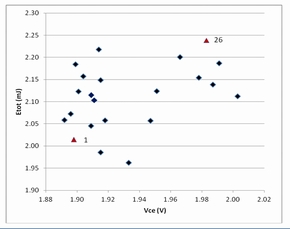

ゲート抵抗の構成オプションをテストするために、22個の部品から2つのIGBTを選びました。この2つはミスマッチを理由に選ばれました。図1は、デバイスのVCE(sat)電圧を横軸に、総スイッチング損失を縦軸にプロットしたものです。

テストに使用したデバイスは、「NGTB40N60IHL IGBT」(オン・セミコンダクター製)であり、600ボルト、40アンペアの仕様です。ユニット1および26は、両方のパラメーターの差異を理由により選ばれており、ターンオン損失は、それぞれ1.65mJ、1.85mJ、ターンオフ損失は、それぞれ0.366mJ、0.390mJでした。

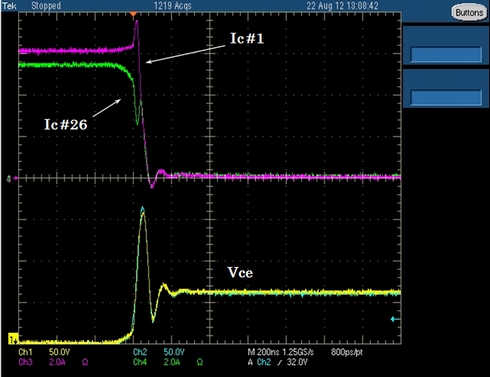

1つのドライバおよび個別の22Ωゲート抵抗を共有した場合、ターンオフ時の電流の波形のアンバランスは明らかです。これは、2つのデバイスの閾(しきい)値、相互コンダクタンスおよび、ゲート容量特性の違いによるスイッチングスピードのミスマッチによるものです。

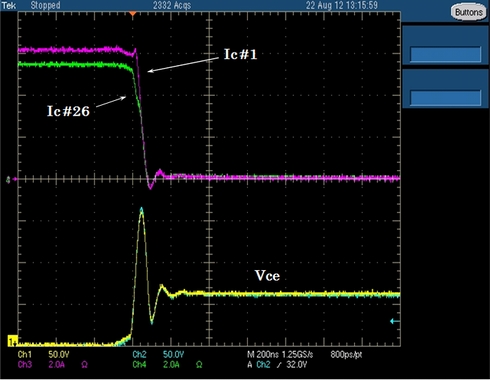

図3は、特定時間にゲートを同じ電位にするよう共通の11Ωゲート抵抗を使ったスイッチング波形を示しています。ターンオフ時のアンバランスは、この構成において大幅に削減されます。2つのスイッチング波形を見て分かるように、DCアンバランスは、ゲート抵抗の影響を受けていません。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentPR

Pickup ContentsPR

Special SitePR

あなたにおすすめの記事PR