2つのICで低リップル、高効率の電源回路を実現:Design Ideas パワー関連と電源(1/2 ページ)

今回は、降圧型のスイッチング電源(SMPS)ICとリニアレギュレーターが抱えるそれぞれの問題点を解決する回路を紹介する。それは、高効率のSMPSを使用し、そのSMPSの出力に含まれるノイズ、リップルをLDOリニアレギュレーターによって低減するという手法である。

降圧型のスイッチング電源(SMPS:Switching Mode Power Supply)ICを使用すれば、電源を効率良く安定させることができる。しかし、SMPSには、スイッチング動作によって出力電圧にリップルが現れてしまうという問題がある。

例えば、RF帯のパワーアンプにノイズが混入すると、帯域内にスプリアス信号や変調ノイズが発生する。そのため、RFシステムをはじめとするアナログ回路を扱う技術者は、リニアレギュレーターのような低ノイズの電源ICを伝統的に好んできた。

リニアレギュレーターは、出力ノイズが小さく、PSRR(Power Supply Rejection Ratio:電源変動除去比)が高い。つまりはクリーンな電圧を供給でき、パワーアンプ用に使用してもアンプの出力に干渉が及ぶことがない。その半面、リニアレギュレーターは、入力電圧の変動によって出力電圧が変動する可能性があるという問題を抱えている。

また、入力電圧と出力電圧の差が大きくなると、消費電力が増加して変換効率が低下する。低ドロップ電圧(LDO:Low Fropout)のリニアレギュレーターを使用する場合でも、ある程度、入出力の電圧差を確保しなければならない。

PSRRは単独で用いる場合よりも上回る

両方式の電源ICが抱えるそれぞれの問題点には次の方法で対処できる。それは、高効率のSMPSを使用し、そのSMPSの出力に含まれるノイズ、リップルをLDOリニアレギュレーターによって低減するという手法だ。

SMPSの出力電圧は、LDOリニアレギュレーターの出力電圧より最小ドロップ電圧分だけ高い値に設定する。このようにすることで、SMPSの出力に含まれるスイッチングノイズが効果的に除去されるとともに、リニアレギュレーターの消費電力も最少になって高い効率を維持できる。しかも、各電源のPSRRが重畳される結果、電源回路全体としてのPSRRは、SMPS、LDOリニアレギュレーターを単独で用いる場合を上回ることになる。

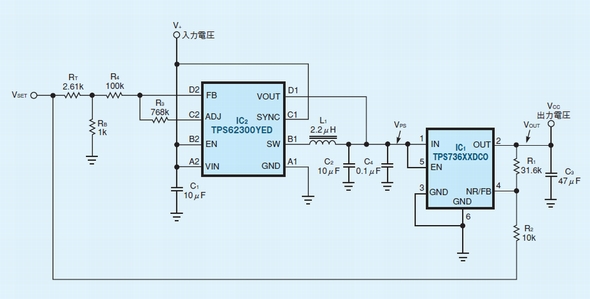

図1に、SMPSの後段にリニアレギュレーターをカスケード接続した電源回路の例を示した。この電源回路の出力電圧は1.5V〜5V、出力電流は400mAである。この例では入力電圧を6Vに固定することを前提としているが、所望の最終出力電圧よりも0.5V以上高ければ任意の電圧を使用できる。

図1:SMPSとLDOリニアレギュレーターを組み合わせた電源回路 (クリックで拡大)

図1:SMPSとLDOリニアレギュレーターを組み合わせた電源回路 (クリックで拡大)IC1がLDOリニアレギュレーター、IC2がSMPS(いずれもTexas Instrumentsの製品)。IC1の製品名中の「XX」はレギュレーターの出力電圧を表す。

抵抗R1とR2、参照電圧VSETによって、LDOリニアレギュレーターの出力電圧、すなわち電源回路全体としての出力電圧が決まる。参照電圧VSETを0V〜1.105Vの範囲で調整すると、最終出力電圧が比例的に変化する。抵抗RT、RB、R3、R4によってVSETが分圧され、SMPSの出力電圧(VPS)がLDOリニアレギュレーターの出力電圧よりも常に0.2V高くなるように制御される。これにより、LDOリニアレギュレーターの消費電力は任意の出力電圧、最大出力電流に対して80mWとなる。

Copyright © ITmedia, Inc. All Rights Reserved.