CPLD回路の電源を自動的にシャットダウン:Design Ideas アナログ機能回路(1/2 ページ)

CPLDは低電力動作モードを備えていることが多い。しかし、電池駆動のシステムでは、そのシステムを使わないときには、わずかな電力さえも使用せず、完全にパワーダウンさせることが目標になる。今回は、CPLDの内部回路と外付け部品によって、電池駆動のシステムに自動パワーダウン機能を持たせた回路を紹介する。

自動パワーダウン機能を持たせた回路

CPLDは低電力動作モードを備えていることが多い。しかし、電池駆動のシステムでは、そのシステムを使わないときには、わずかな電力さえも使用せず、完全にパワーダウンさせることが目標になる。

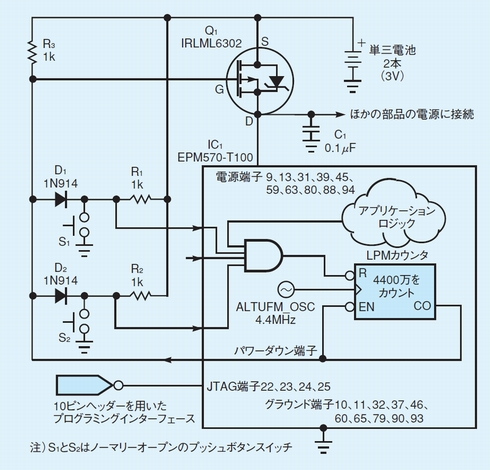

図1に示したのは、CPLDの内部回路と外付け部品によって、電池駆動のシステムに自動パワーダウン機能を持たせた例である。図中のpチャンネルMOSFET(Q1)には、米International Rectifier社の「IRLML6302」または同等品を使用する。このMOSFETは、CPLD(IC1)やその他の部品の電源制御スイッチとして機能する。Q1のソースはバッテリーの+端子に接続し、ドレインはCPLDの電源端子とパワーダウン制御が必要なほかの部品の電源に接続する。Q1のゲート電圧は、CPLDとスイッチアレイ(S1、S2)で制御し、ユーザーがスイッチを押すと、ゲートにバイアスがかかってQ1がオンする仕組みだ。これにより、CPLDやほかのコンポーネントに電源電圧が供給される。

一方、CPLD(Altera社の「EPM 570-T100」)には、スイッチとシステムの動作を監視するタイマーが組み込まれている。これにより、システムが非アクティブな時間が一定以上経過すると、タイマーからの信号によってQ1が自動的にオフする。その結果、Q1に接続されているCPLDなどの部品がパワーダウンするようになっている。

S1、S2が共にオフ(オープン)になると、1kΩのプルアップ抵抗R3がゲート-ソース間の電位差を0Vで維持することで、Q1はオフに保持される。IC1の電源をオフにすると、IC1のパワーダウン端子を介してグラウンドへのリークパスが形成される。しかし、EPM570-T100には、ユーザーがアクセス可能なI/O端子からの電流を300μA未満に制限するホットソケット保護機能が備わっている。そのため、ワーストケースでも、Q1のゲート電圧が閾(しきい)値に達してしまうことはない。

いずれかのスイッチを押した場合

続いて、いずれかのスイッチを押したときの動作だが、その場合、そのスイッチに対応するダイオードからの電流パスが形成され、Q1にはR3を介して約2.3Vのゲート‐ソース間バイアスがかかる。これだけの電位差があれば、約100マイクロ秒でQ1がオンしてIC1をパワーオンできる。機械的なスイッチは3ミリ秒もあればオンになるが、人が「押して、離す」操作は30ミリ秒以上かかる。

そのため、ユーザーがスイッチを離すまでに、IC1をオンにして内部回路をリセットし、パワーダウン信号の論理を0にすることができる。これにより、ユーザーがスイッチを離しても、Q1はオンしたままとなり、IC1に電源電圧が供給され続ける。

非アクティブな状態が続いた場合

この回路を、その後何も処理が行われず非アクティブな状態が続いた場合に、自動パワーダウン機能が働くようにするとしよう。この機能を実現するためには、CPLDに電源制御ロジックを1つ追加する必要がある。その回路は、Alteraの開発ツール「Quartus IIソフトウェア」によって実現できる。IC1は4.4MHz±25%の発振回路altufm_oscを内蔵しているので、これがLPM(ライブラリパラメタライズドモジュール)であるモジュロ4400万カウンターを駆動するようにする。

このカウンターは、ユーザー独自のアプリケーションロジックからローの信号が出力されるか、あるいは任意の外部スイッチがオンするとリセットされる。すると、カウンターのキャリーアウト(CO)がローになり、パワーダウン端子にもローが出力される。

スイッチが全て開いたままの状態でアプリケーションロジックが非アクティブになると、カウンターは約10秒で4400万までカウントし、キャリーアウト信号がハイになる。それによりカウンターの機能が止まり、キャリーアウト信号はハイに保持される。このとき、パワーダウン端子にもハイが出力されるわけだが、その電圧が2.3Vに達した時点でQ1がオフする。IC1に電源電圧が供給されなくなると、パワーダウン端子はトライステート(あるいは切断)モードに入り、R3によってゲート電圧がプルアップされてQ1はオフのまま保たれる。

Copyright © ITmedia, Inc. All Rights Reserved.