CPLD回路の電源を自動的にシャットダウン:Design Ideas アナログ機能回路(2/2 ページ)

応用的な事柄に触れる

ここまでが自動パワーダウン機能の概要だが、ここで少し応用的な事柄についても触れておく。EPM570-T100は、ダウンロードケーブルを10ピンヘッダに接続することにより、JTAG準拠のコマンドを使って各種の設定が行えるようになっている。

その際には、設定前、設定中、そして設定直後に外部スイッチを押し、CPLDに電源電圧が正しく供給されるようにする必要がある。なお、電源、グラウンド、JTAG信号用には特定の端子を使用するが、スイッチからの入力とパワーダウン出力には任意のI/O端子を割り当てることが可能である。

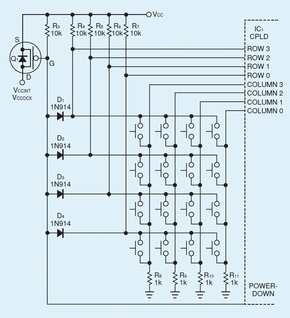

また、プッシュボタンスイッチが多数必要な場合は、n個のダイオードを使用するだけで、n×mのスイッチのマトリックスを構成できる。図2の例では、ダイオードD1〜D4を介してスイッチ行をMOSFETのゲートに接続している。抵抗R8〜R11は各スイッチ列からグラウンドへのパスとして働くが、各列に対応する信号(COLUMN0〜COLUMN3)をローに保持することで消費電流を最小限に抑えるようにしている。一方、LPMカウンタによるタイマーは、各行に対応する信号(ROW0〜ROW3)によってリセットされる。

ここでいずれかのスイッチを押すと、Q1のゲートにローレベルの電圧が加わり、CPLDがパワーオンする。パワーアップルーティンが十分に高速であれば、アプリケーションはスイッチのマトリックスの行と列をスキャンして、スイッチを離すまでにどのスイッチが押されたのかを判断するといったことが可能である。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルター回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバー】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事から200本を厳選し、5つのカテゴリーに分けて収録した。

関連記事

周波数を調整できる高周波ノッチフィルター

周波数を調整できる高周波ノッチフィルター

今回は、8ピンパッケージのデュアルオペアンプICと、8ピンパッケージのスイッチドキャパシター帯域通過フィルターを使ったノッチフィルターを紹介する。 応答速度が高くリップルが低い包絡線検出回路

応答速度が高くリップルが低い包絡線検出回路

複雑なオーディオ信号波形から振幅に関する情報を取り出すことができる包絡線フォロワー回路で、信号の急激な減衰にも対応できる回路を紹介する。【修正あり】 過電流/過電圧保護用のブレーカー回路

過電流/過電圧保護用のブレーカー回路

今回は、少数の低価格な部品で構成されているが、電流/電圧のいずれかが設定条件を超えると的確に電源を遮断し、過電流/過電圧に対するブレーカーとして機能する回路を紹介する。 振幅制御機能を備えたGIC発振回路

振幅制御機能を備えたGIC発振回路

古典的なGIC(一般化インピーダンス変換器)に基づく回路である。固有の振幅安定化機能を備えた正弦波発振回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.