モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編I】:レファレンスモデルからFPGA用サブシステムの作成まで(6/7 ページ)

コラム1:テストハーネスを作成するSimulink Test

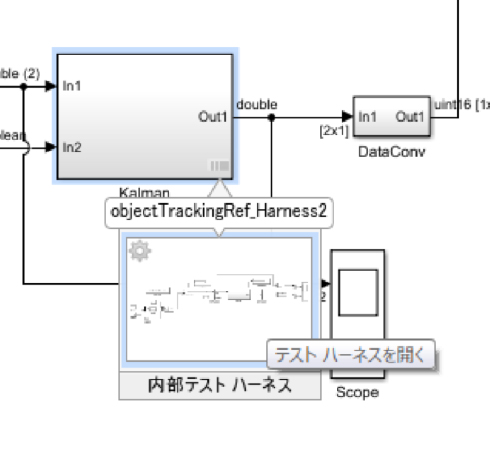

ここで使用している各サブシステムは、Simulinkのオプション「Simulink Test」を使って単体検証を行っています。Simulink Testを使うことで、サブシステムに対して、単体テストハーネスを作成することができるため、さまざまなテストパターンを使用した検証や、パラメーターチューニングが容易に素早くできるようになります。単体テストハーネスと全体モデルはリンクされているので、どちらかを変更すると、他方にも変更が反映されます。また、単体テストハーネスは親モデルのファイル内に保存されていて、図B-1に示すようにサブシステムの右下にあるリンクから開けるため、単体テストハーネス~親モデル間の行き来も容易に行えます。

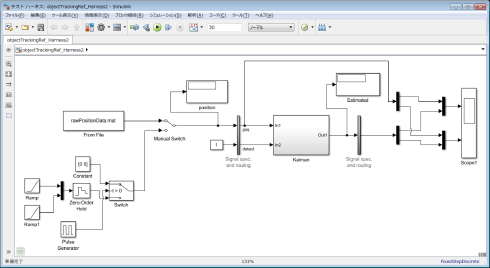

単体テストハーネスモデルを図B-2に示します。

コラム2:FPGA実装用画像処理ライブラリVision HDL Toolbox

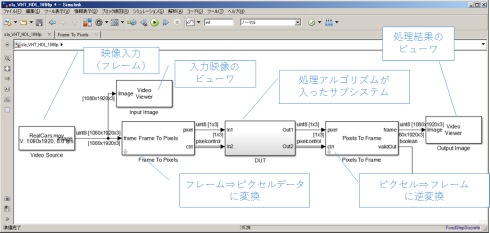

Vision HDL Toolboxはその名の通り、ビジョンアルゴリズムからHDL生成するためのMATLAB/Simulinkのオプション製品です。この製品はフィルター、フォーマット変換、モルフォロジーなどの各種画像処理ライブラリーが提供され、ライブラリーを使用することで、アルゴリズムの開発とFPGA、ASIC実装を早期に実現できるようになっています。ライブラリーのフォーマットはSimulinkブロックとSystem Objectですので、ブロック線図とコードでの記述両方に対応しています。

Vision HDL Toolboxのブロックは、FPGA内での処理と同様ピクセルベースの処理を行うようになっています。Vision HDL Toolboxを使って、どのようにモデルを作れば良いのかイメージを持ってもらうために、簡単なモデル例を図C-1に示します。基本的なシミュレーション用の機能はブロックライブラリーで提供されているので、それを並べて信号フロー通りに結線します。Frame To Pixelブロックで、フレームデータをピクセルデータに変換すると、水平・垂直同期やValidなどのコントロール信号が追加されます。これはFPGAの内部処理において必要な信号であるため、変換ブロックで自動的に付加されるようになっています。

Vision HDL Toolboxのコントロール信号

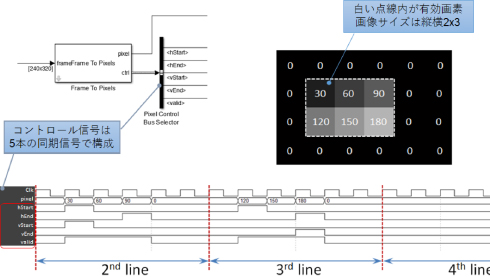

FPGAやASICで画像処理を行う際には、ピクセルストリーム信号の他にコントロール信号が使われます。Vision HDL ToolboxのFrame To Pixelsブロックを使って、フレームベースの信号をピクセルストリーム信号に変換できます。図C-2に、縦横2×3の小さい画像を例にしたコントロール信号のタイミングチャートを示します。

MATLABプログラムやSimulinkのフレームベースのシミュレーションでは、任意のピクセルに対する処理を、画像の行列番号に相当する座標位置を指定することで行えますが、ピクセルストリーム信号では、現在入力されている信号がどこの画素に相当するかを知るためには、このコントロール信号を使用します。hStartでイニシャライズして、valid信号で有効化されるカウンタを使うと、横方向のピクセル位置を把握することができ、同様にvStartでイニシャライズして、hStartで有効化すれば、縦方向のピクセル位置を把握できます。

Copyright © ITmedia, Inc. All Rights Reserved.

図B-1:サブシステムをクリックしてテストハーネスを開く様子

図B-1:サブシステムをクリックしてテストハーネスを開く様子