モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編I】:レファレンスモデルからFPGA用サブシステムの作成まで(7/7 ページ)

コラム3:固定小数点シミュレーション用オプションFixed-Point Designer

FPGAでは多くの場合、固定小数点演算が行われます。それは回路面積低減、消費電力低減、演算速度向上のメリットがあるからです。MATLABとSimulinkでは、それぞれFixed-Point Designerを使うと固定小数点演算を行うことができます。例を見てみましょう。

データ型を定義せずに計算を行うと、結果はdouble型(64ビット浮動小数点)となります。

>> A = 1/3

A =

0.3333>>

>> class(A)

ans =

double

固定小数点データ型を使う場合はコマンドfiを使って、fi(値、符号の有無、ビット幅、小数部のビット幅)の順に引数を与えます。

>> B = fi(1/3, 1, 8, 7)

B =

0.3359

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 8

FractionLength: 7

>> class(B)

ans =

embedded.fi

固定小数点データ型同士の演算では、結果も固定小数点データ型となります。

>> B*B

ans =

0.1129

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 16

FractionLength: 14

バイナリや16進表示も可能です。

>> B.bin ans = 00101011 >> B.hex ans = 2b

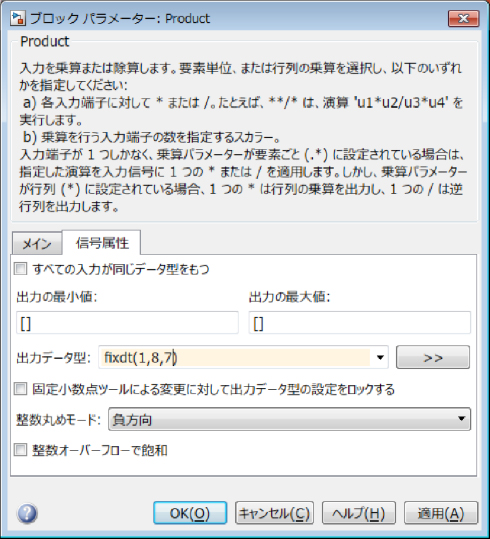

Simulinkでも同様に、図D-1のように各ブロックパラメーターの信号属性タブで固定小数点データ型(符号の有無、ビット幅、小数部のビット幅、丸めモード、オーバーフロー時の飽和処理の有無)を設定することができます。

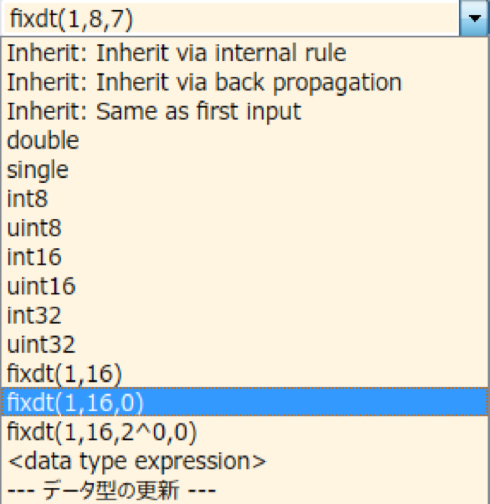

Simulinkにおける固定小数点設定は、手前や後ろに接続されるブロックでのデータ型を継承する設定がデフォルト値になっています。そのため、全てのブロックで行う必要がなく、設定は非常に楽に行えます。また、継承する方法も、手前に接続されているブロックから継承したり、後に接続されているブロックから継承したり、手前のブロックのデータ型と同じにしたり、図D-2に示すようにいくつかあります。

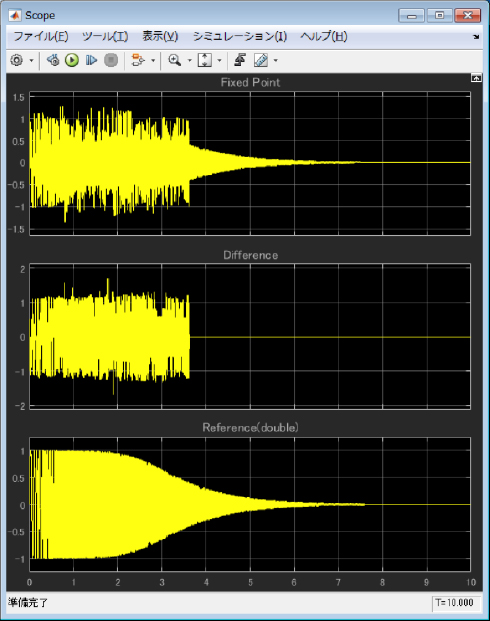

固定小数点化したモデルでシミュレーションを行うと、実機に実装する前に、オーバーフロー解析、打ち切り誤差などの解析が可能です。図D-3に示したフィルターモデルのシミュレーション結果波形では、入力されるデータレンジに対して、ビット幅が足りないためオーバーフローが生じています。

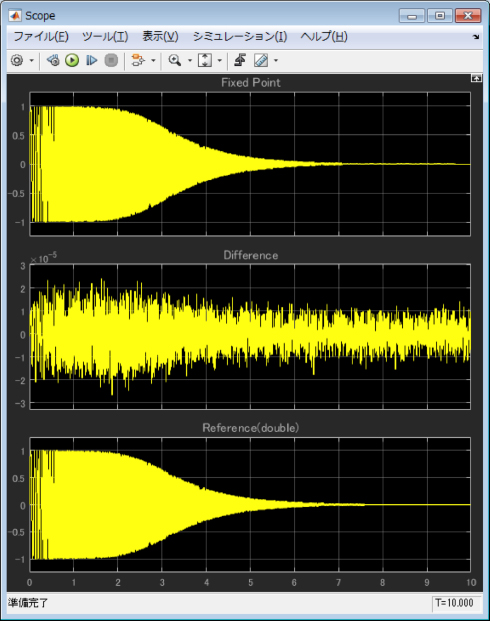

この修正は、オーバーフロー箇所発生を探し出し、必要なビット幅を計算、修正し、他に悪影響を与えないか再度シミュレーションを行って確認するという労力の掛かる作業です。しかし、Fixed-Point Designerの機能「固定小数点ツール」は、ビット幅を自動的に最適化することができます。これを実行することで、自動的にビット幅が最適化され、図D-4のようにオーバーフローが解消しました。

(次回に続く)

著者

松本 充史:MathWorks Japan アプリケーションエンジニアリング部 プリンシパルアプリケーションエンジニア

関連記事

モデルベースデザイン手法を使ったProgrammable SoCの協調設計【準備編】

モデルベースデザイン手法を使ったProgrammable SoCの協調設計【準備編】

今回から数回にわたり「モデルベースデザイン手法を使ったProgrammable SoCの協調設計」とはどのようなものか、実践を交えて解説していきます。第1回は、CPUコアを備えたFPGAであり、ソフトとハードを協調動作できるProgrammable SoCにモデルベースデザイン手法を用いる利点を中心に紹介します。 モデルベース開発ツールを使いこなせ

モデルベース開発ツールを使いこなせ

組み込みシステム開発チームは、新製品をいかに早く市場に送り出すかでしのぎを削っている。そのための方策として、設計者らはモデルベースの開発ツールに目を向け始めている。ますます複雑になるソフトウエア開発を迅速に行うためだ。そうしたツールの多くは、UMLをベースとしている。 最新ツールが支えるモデルベース設計

最新ツールが支えるモデルベース設計

組み込みシステムの大規模化、複雑化が進むに従って、ソフトウエア開発の負担が大きくなってきた。そこで数年前から注目されてきたのがモデルベース設計である。本稿では、モデルベースのソフトウエア開発をサポートするために、どのようなツールが開発されており、どのように活用されているのかを紹介する。 「MATLAB」ファイルからHDLコードを直接生成、新オプションでHDL対応を拡充

「MATLAB」ファイルからHDLコードを直接生成、新オプションでHDL対応を拡充

モデルベース設計環境「MATLAB/Simulink」の新バージョン「R2012a」の発表に合わせて、HDLに対応する新オプションが2つ追加された。「HDL Coder」は「MATLAB」ファイルからのHDLコードを自動生成が可能。「HDL Verifier」は、MATLABファイルや「Simulink」モデルに加えて、手書きのHDLコードをFPGAの評価ボードに実装して、検証作業を行うことができる。 「MATLAB/Simulink」の新バージョン「R2010b」、信号処理/通信機能向けの機能を強化

「MATLAB/Simulink」の新バージョン「R2010b」、信号処理/通信機能向けの機能を強化

Copyright © ITmedia, Inc. All Rights Reserved.

図D-1:プロックパラメーターの信号属性タブ

図D-1:プロックパラメーターの信号属性タブ 図D-2:データ型のドロップダウンリスト

図D-2:データ型のドロップダウンリスト