PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために:高速シリアル伝送技術講座(1)(5/5 ページ)

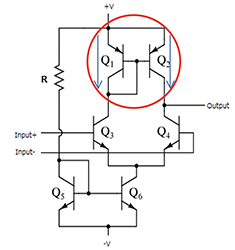

オペアンプの初段で使用されているカレントミラー回路は図12の上部の赤丸です。カレントミラー回路の特徴はQ1とQ2のトランジスタは同一シリコン上に形成されるため同等特性で、ベース電流がQ1とQ2接続され同じため、Q1に流れる水色矢印の電流(エミッタ・コレクタ間)の大きさは、鏡に映すようにQ2の水色矢印に流れる電流と等しくなります。

またQ3とQ4も同特性のトランジスタとなるため、Input+とInput−の入力に電圧差があると、Outputにその差が計算され出力されます。

下部にもカレントミラー回路Q5、Q6がありますが、抵抗RでQ5とQ6に流れる電流を決めています。これは一般的な定電流源の構成の1つで、図8(2)のLVDSドライバ上部の3.5mA定電流源部や図11(2)レシーバーの下側のVbiasと書かれたトランジスタ部も同様です。

図12はPNP、NPNのバイポーラトランジスタの構成ですが、図11(2)のPMOS、NMOSのCMOSのLVDSレシーバー等価回路とほぼ同じ構造なのが分かります。

この図12カレントミラー差動増幅器は、入力+/−の終端抵抗部に数十ミリボルト程度の微細な電位差があれば、問題なく増幅するアナログの増幅器です。そのため、PMOS−NMOSのロジックバッファ回路(図10)と基本的に動作が異なっています。

このアナログの差動増幅器を使用することで、デジタルCMOSロジックでは不可能だった小振幅で高速なデジタルの1、0信号を受信できるようになりました。

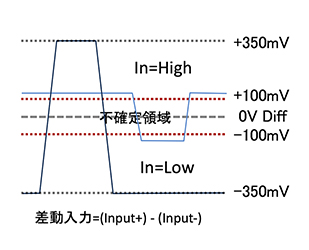

このアナログの差動増幅器の構造は、各規格が採用しているCML、LVDSのレシーバー、また高速のDDR2、DDR3で使用されるSSTL入力バッファと基本的に同じです。高速、小振幅の受信部ではこのアナログの差動増幅器が活躍しています。図13はLVDSの差動入力スレッシュホールドを表しています。LVDSでは±100mV以上の差動入力があれば、論理値が確定するため、青色線の小振幅信号でも正しく1、0を受信可能です。

小振幅送信、高い感度の受信、その他の要素

送信側は定電流駆動による小振幅のドライバ、受信側は小振幅で動作が可能なアナログのレシーバーがそろいました。これより送受信の環境がそろい、高速差動信号伝送が実現できそうです。

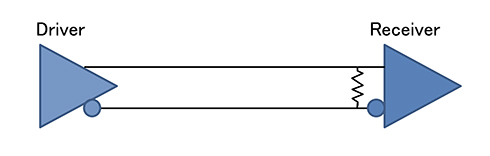

ところで図14のドライバ・レシーバーの構成で、他に必要な要素は何でしょう?

もう1つ、とても重要な要素として伝送路があります。次回は、差動信号伝送の特徴や使用されている技術、注意点について説明していきます。

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

関連記事

HDMI 2.0のできること

HDMI 2.0のできること

映像/音声の伝送規格として定着したHDMIの最新規格「HDMIバージョン2.0」(以下、HDMI 2.0)がこのほど策定された。ここでは、これまでのHDMI規格バージョンとHDMI 2.0ではどのような違いがあり、どんなことができるようになったのかみていく。 SLVSインタフェースをFPGAで活用せよ

SLVSインタフェースをFPGAで活用せよ

SLVSは、データ信号を高速かつ低消費電力で伝送する用途において、LVDSに替わって利用される機会が増加しているデータ伝送規格である。FPGAにSLVSを実装する場合には、LVDSを実装する場合とは異なるさまざまな知見が必要になる。本稿では、SLVSの概要と、FPGAにおける応用例を紹介する。 長距離高速伝送が可能、LVDSインタフェース搭載のLEDドライバ

長距離高速伝送が可能、LVDSインタフェース搭載のLEDドライバ

ザインエレクトロニクスは、LVDSインタフェースを搭載したLEDドライバ「THL3512」「THL3514」を発表した。LVDSシリアルインタフェースを用いた制御により、高速・長距離伝送と高ノイズ耐性を可能にした。 インターフェースIC活用のススメ

インターフェースIC活用のススメ

ロジックICの電源電圧の低下に伴い、インターフェースICの重要性が増してきた。現在では、単なる負荷駆動の手段ではなく、より効率が良く、より安全な信号伝送の手段としてその価値は高まってきている。本稿では、まずインターフェース回路の基本を再確認した上で、各種インターフェースICの果たす役割や最新の製品動向を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

図14:差動信号伝送 基本トポロジ

図14:差動信号伝送 基本トポロジ