PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために:高速シリアル伝送技術講座(1)(4/5 ページ)

LVDS(Low Voltage Differential Signaling)の登場

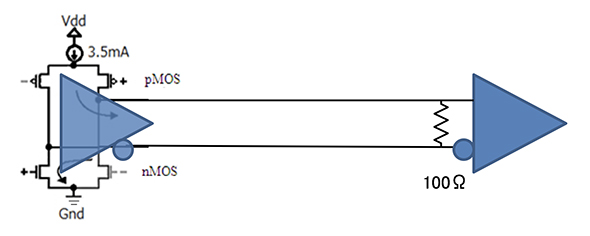

前項で説明した小振幅と差動伝送の方式を採用し高速化を図ったのがLVDS(Low Voltage Differential Signaling)です。エッジレートは1V/1ナノ秒程度と当時のCMOS/TTLのそれと変わりません。LVDSは3.5mAの定電流源で100Ω終端時350mVの小振幅ながら、最大転送速度は規格仕様で655Mbps、メーカー仕様で最大3Gbpsまで実現し、高速転送を低消費電力でサポートしています。CML(Current Mode Logic)はLVDSよりも大きい標準振幅800mVで消費電力は大きいですが、エッジレートが速くより高速になります。

このLVDSは1994年に物理層の製品が発売され、その後1995年にANSI/TIA/EIA-644-A LVDSとして承認されました。

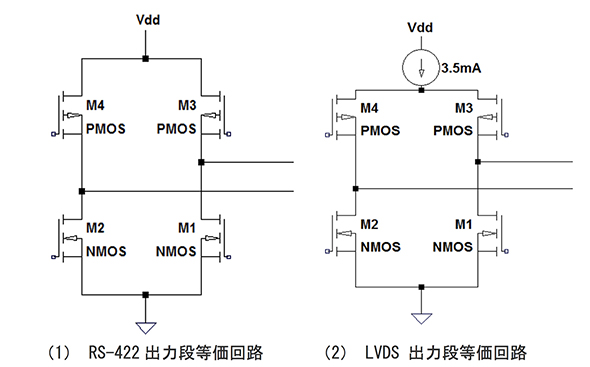

図8の左側(1)がRS-422のドライバ等価回路、図8の右側(2)がLVDSのドライバ等価回路です。

RS-422ドライバとLVDSドライバの出力段等価回路はほぼ同じ構成となっていて、どちらも差動の伝送方式を採用しています。違いとしては図8右側LVDSドライバには定電流源が配置されています。LVDSはこの定電流源駆動により電流の流れる経路の電流値を制限し、図9右側の受信端で100Ωの終端抵抗を配置した場合はI=3.5mAのためV=IRより、レシーバーの入力端で350mVの小振幅となります(終端抵抗値は伝送路の特性インピーダンスに合わせます)。

前項でトグルスピードの高速化のために振幅を下げることが有効と説明しましたが、LVDSでは当時の汎用的なプロセスで小振幅とすることで高速化を行いました。

これで送信側の高速化は達成できたようです。しかし振幅が小さいことは受信側の性能に問題にならないのでしょうか? そこでCMOSの一般的なシングルエンドの入力ロジック等価回路とLVDSレシーバー等価回路を比較してみましょう。

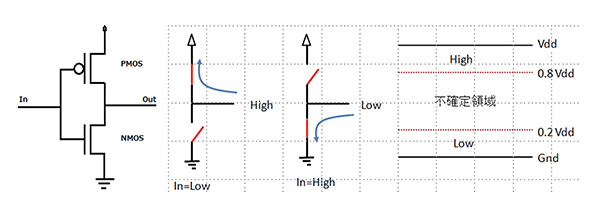

図10は一般的なPMOS−NMOSコンプリメンタリ構成のCMOS入力ロジックです。In信号がLowのとき上側のPMOSはオン、下側のNMOSはオフ状態となり出力Highになります(図10の左)。In信号がHighのときPMOSはオフでNMOSはオン状態、出力Lowとなります(図10右)。

上部PMOSと下部NMOSのスイッチング特性の制限からIn信号の入力HighがVccx0.8以上(Vih)で出力Lowが確定、入力LowがVccx0.2以下(Vil)で出力Highが確定などと規定され、その場合中間の0.2〜0.8は不確定領域になります。これが一般的なロジック回路のインプットVih/Vil特性でデジタル系半導体のデータシートによく記載されている内容です。

それではLVDSのレシーバーの構成ではどうでしょうか。

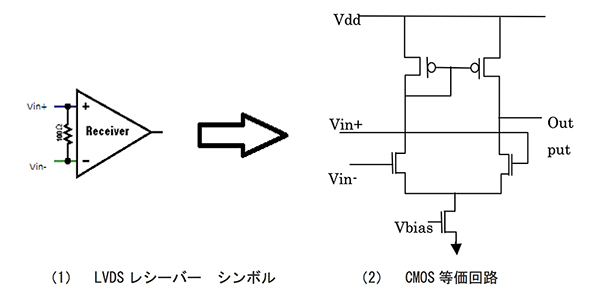

図11(1)がLVDSレシーバーのシンボル、図11(2)が入力段のCMOS等価回路です。

LVDSレシーバーの等価回路は図11(2)のようにカレントミラー差動増幅器で構成され、+と−入力信号の差を計算し後段へ出力します。このカレントミラー差動増幅器は、オペアンプやコンパレーターICの入力段で採用され、シンボルはこれらアナログICと同様に三角形で表現されています。この差動増幅器を使用したオペアンプIC(Integrated Circuit)の歴史はとても古く、1960年代にこの構造のIC製品が開発され、アナログ半導体メーカーから数多くの製品が販売されています。

アナログ信号を扱うアプリケーションではオペアンプやコンパレーターの機能が必ず使用されていると言ってよいでしょう。

Copyright © ITmedia, Inc. All Rights Reserved.

図9:LVDS TX/RX接続方法

図9:LVDS TX/RX接続方法