終端方式と高速シリアルI/Fデバイス:高速シリアル伝送技術講座(5)(1/3 ページ)

今回は、LVDS、CML/PECL、計測器などの終端方法と、シリアル伝送デバイスの種類について解説します。

終端抵抗と特性インピーダンス

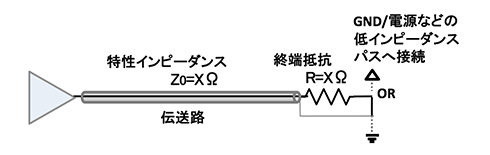

伝送路の終端に、連載第4回で説明した伝送路の特性インピーダンスZ0=XΩと同じ値の抵抗を付けると、信号のエネルギーが終端部で吸収され、高速化を阻害する要因の1つである反射を防げます(図1)。終端抵抗は差動100Ωやシングルエンド50Ωが一般的ですが、これらは固定値ではなく伝送路特性インピーダンスに合わせた抵抗値の終端を使用します。

反射のない信号伝送には伝送路の特性インピーダンスに合わせた終端抵抗が必要になりますが、シングルエンド信号の振幅3.3Vや1.8Vの信号で終端抵抗を使用すると、終端抵抗部で消費される電力はW=V2/Rとなり電圧の2乗で増大します。そのため信号終端部の反射によるリンギングが次のサイクルまでに安定する低速シングルエンドの信号伝送では、受信部での終端抵抗は使用しないことが一般的です。リンギングを抑える手法として、出力矩形波のエッジレートを下げ、信号に含まれる高周波数成分を低減する方法もありますが高速化が困難になります。

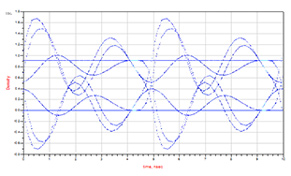

高速のシリアル伝送では1ビット時間が1Gビット/秒(bps)では1ナノ秒、10Gbpsでは100ピコ秒となり、この1ビット時間と比較すると伝送路でのインピーダンスミスマッチよる多重反射(連載第3回参照)は安定するまでに長い時間がかかります。例えばPCBマイクロストリップライン4cmの差動伝送路で、小振幅差動としては低速の200Mbpsの信号を流した場合でも、終端抵抗がないと図2のように反射を繰り返しアイパターンのEYEが開口しません。

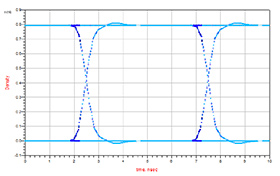

高速シリアルデバイスのデータシートなどで記載されている送信波形は、図3のようなきれいなEYEですが、これらは最適に終端された条件で測定されています。ここでは高速信号伝送でシグナルインテグリティー(Signal Integrity/信号品質)の要となる各種終端方式について説明していきます。

さまざまな終端方法:LVDS、CML/PECL、計測器などの終端

終端の基本的な考え方

最近では、PCなどの民生製品でも10Gbpsクラスの高速伝送規格の採用が増えてきましたが、どの高速規格でも最適な終端はシグナルインテグリティーの最も重要な課題です。物理層が異なると終端方法に多少の違いがありますが、一般的に受信回路はハイインピーダンスのため、伝送路の特性インピーダンスに合わせた終端抵抗を使用し反射を防いでいます。信号終端部分に終端抵抗を配置し、片方を低インピーダンスパスに接続する、という構成であればよく、ドライバー/レシーバー回路が最適に動作する電圧に終端しています。以下に、代表的な終端方法と特長を説明していきます。

受信側 ― Vcc/GNDへの終端

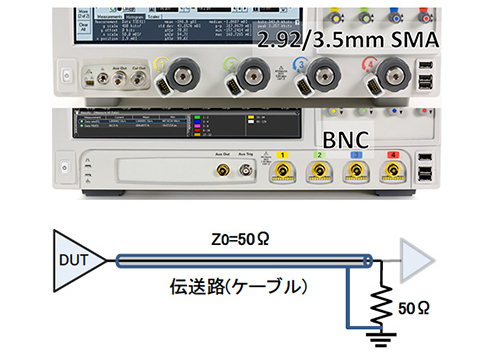

受信端の信号ラインに終端抵抗を介してVccやGNDに接続する方法です。ケーブルやPCB配線などのシングルエンド伝送路の一般的な特性インピーダンスに合わせて50Ω終端が使用されています。50Ωの終端では、使用するケーブル、コネクターのインピーダンスもシングルエンド50Ωの製品を選びます。

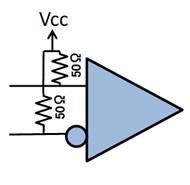

CML(Current Mode Logic)の受信端では、シングルエンドの場合は電源Vccに対して片方50Ω、各種高速伝送規格で採用されているディファレンシャルでは図4のように+/−とも50ΩでVccに終端されています。

測定器などで使用されているBNC、SMA、N型などコネクターのシングルエンド信号入力は図5のように内部で50Ωに終端されています。そのため測定には特性インピーダンス50Ωのケーブルを接続します。

またSMAコネクター互換の2.92mmや3.5mmの50Ωインピーダンスコネクターは30GHz以上の帯域があり、高周波特性に優れているため伝送路として最適です。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:伝送路の終端方法

図1:伝送路の終端方法

左=図2:伝送距離4cm、200Mbps、終端なし / 右=図3:伝送距離4cm、200Mbps、終端あり

左=図2:伝送距離4cm、200Mbps、終端なし / 右=図3:伝送距離4cm、200Mbps、終端あり 図4:CML差動入力/50Ω、Vccへの終端

図4:CML差動入力/50Ω、Vccへの終端 図5:BNC、SMA(2.92/3.5mm)コネクター部/50Ω、GNDへの終端

図5:BNC、SMA(2.92/3.5mm)コネクター部/50Ω、GNDへの終端