RISCとCISC、それぞれの命令処理方式:ハイレベルマイコン講座:【アーキテクチャ概論】(3)(2/4 ページ)

【2】スーパースカラ

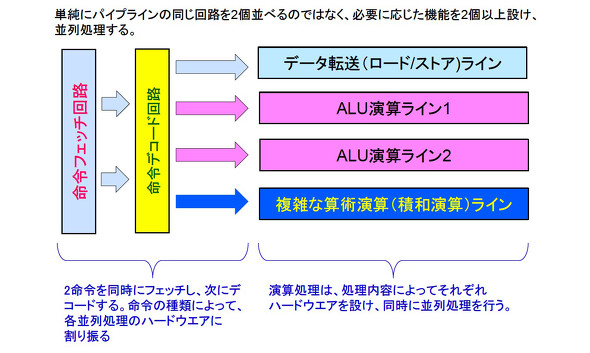

スーパースカラは、パイプライン処理のハードウェアを複数個並べて、同時に複数の命令を実行する方式だ。ただし、単純に同じ回路を複数個並べると論理規模が大きくなって効率が悪いので、必要に応じた機能を複数個並列処理する。図3にスーパースカラの概念図を示す。命令をフェッチする回路は複数命令分を同時に行うようになっている。命令デコード回路も複数命令を同時にデコードするようになっている。

データ処理のハードウェアに関しては、処理内容に応じて異なる処理のハードウェアが準備される。例えばデータを転送するだけのロード/ストアー命令にALU(Arithmetic and Logic Unit)は必要ないので、ALUと別経路でのハードウェアを設ける。また、複雑な算術演算(積和演算など)はALUだけでは実行できないので、別のハードウェアを設けてALUとは並列に演算するようにする。

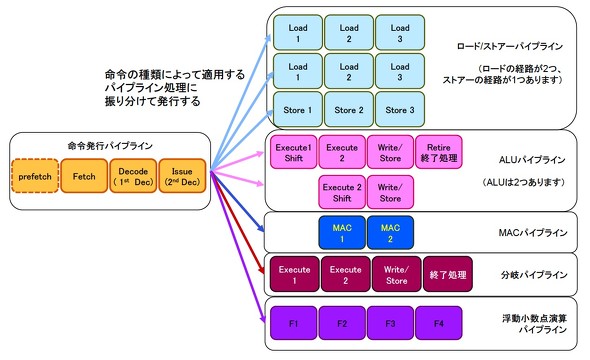

Arm Cortex-M7プロセッサを搭載したSTマイクロエレクトロニクスのマイコン「STM32F7シリーズ」を使って、具体的なスーパースカラを説明する(図4)

デュアルのスーパースカラなので、ALUが2つある。命令コードを64ビット(32ビット命令×2)でフェッチしてきて、2命令を同時にデコード(Decode)し、デコードした結果を、2つのALUに発行(Issue)する。そして同時実行する。

命令をフェッチしてからデコードするまでは3段のパイプライン処理だ。デコード処理は2段になっていて、最初のデコードはそのままデコードと呼ばれるが、2つ目のデコードは発行と呼ばれている。デコードした命令を後段の実行パイプラインに発行する役割を担っているためだ。

論理演算命令(シフト含む)と算術演算命令はALUが実行するが、その他の命令は専用のパイプラインが用意されていて、他のハードウェアが実行する。デコードされた命令の種類によって各パイプラインへ振り分けられる。そして、これらも並列処理される。ロード/ストアー命令はロード/ストアーパイプラン、複雑な積和演算命令などはMACパイプライン、浮動小数点演算は浮動小数点演算パイプラインで行われる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング