電力管理と機能安全でもNoCに勝るものなし:NoCとは(3)(2/2 ページ)

安全性に関する要求

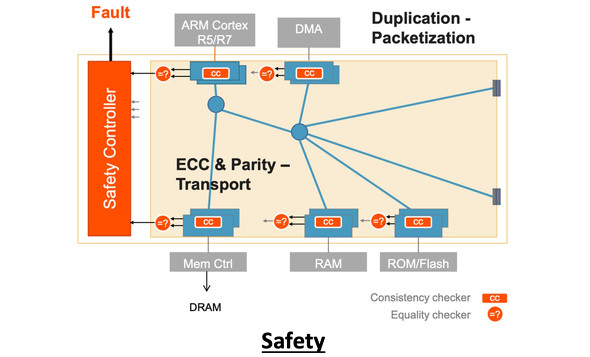

ある意味では、安全性についても同じような図式が当てはまります。IPについては、エンジニアたちは安全リスクを緩和するためのテクニック(誤り訂正符号、パリティ、ロックステップ、三重冗長構成)を考慮しながら安全分析を行います。インターコネクトについてはどうなのでしょう? 高度なNoCテクノロジーではこれらと同じ緩和オプションがサポートされているため、NoC内においてもIPおよび、サブシステム内とまったく同じように故障モード影響診断解析目標を達成することができます。

Fail-operational(故障時動作継続)性能が要求されているASIL-D準拠の設計向けにはさらに興味深い機能があります。Fail-operationalについて、ここで簡単に付け加えておきます。Fail-operationalデバイスは低レベルの問題を監視しなければならないだけでなく、「航行中」のデバイス内におけるIPの正常動作を検証できなくてはなりません。未解決の問題が検出された場合には、誤動作している機能をオフラインにし、問題をドライバーに報告する一方で、故障していても依然として自宅までの走行を可能にしなくてはなりません。これは、ASIL-D準拠が不可欠な先進運転支援システムや自動運転技術で要求される、新しいレベルの安全性能です。

Arteris IP NoCはこの一段と厳格な要求に応えています。設計内のIPは、IPをネットワークに接続している各ネットワークインターフェースユニット(NIU)でNoCから分離することができます。これには電力分離のときと同じメカニズムが使用されています。ひとたび分離されると、ASIL-D準拠の安全コントローラが当該IPに対するLBIST(Logic Built-In Self-Test)チェックをトリガーして正常動作を検証します。問題が検出されると、当該IPは分離されたまま、安全コントローラが問題を報告します。当該IPがLBISTテストに合格すれば、再度有効にしてネットワークに戻すことができます。NoCのこの機能があれば、このレベルの分離とテストが可能になります。そもそもNoCには分散的な性質があるため、すべてが絡み合っているために接続コンポーネントのどれか一つでも故障すると回復に多大な時間を要するクロスバーのような中央インターコネクトに比べ、故障に対してはおのずとより優れた頑強性と耐性を実現できます。

NoCはすべてを叶える

NoCがSoCインターコネクト分野を支配しつつある理由はもはや明白です。私はこの連載の第1回記事で、商用IP市場の成長が、ディファレンシャブルなSoCを作成、構成するための「つまみとダイヤル」としてNoCインターコネクトが使用される制御点を生みだしたと説明しました。これが、私のそれほど大げさでもない「NoCこそがSoCである」という主張につながったわけです。さらに連載第2回では、いかにNoCテクノロジーが、サイズや複雑さに関係なくあらゆるSoCのクロスバーベースのインターコネクトに勝っているかということを説明しました。

そして本記事では、電力管理や機能安全など、これまでのクロスバーベースのインターコネクトでは実現不可能な機能がいかにNoCテクノロジーによって可能になるかということに焦点を当ててきました。結局のところ、モダンSoCを作っている設計チームにとっては(それが大規模データセンターのAIアクセラレータであろうと、絶えず少量の電力を消費し続けているIoTセンサーであろうと)、SoCアーキテクチャを実装し、内部のデータフローを最適化するための鍵を握るのはNoCインターコネクトテクノロジーだということです。

【著:Benoit de Lescure/Arteris IP 最高技術責任者(CTO)】

関連記事

なぜNoCがクロスバースイッチに取って代わったのか

なぜNoCがクロスバースイッチに取って代わったのか

インターコネクト機能として単純なクロスバー方式を採用するという選択もあり得るでしょう。しかしシステム内のエレメントの数が増え始め、さらにエレメント間の距離が意図されたクロック周期に対して長くなってくると、クロスバーではもはやどうにもならず、NoC(Network-on-Chip)方式を採用する必要があります。 NoC(Network-on-Chip)こそがSoCである

NoC(Network-on-Chip)こそがSoCである

NoC(Network-on-Chip)とはどのようなものか。これから複数回にわたり考察していきます。 複雑なSoCでのタイミング収束を短期に済ませる秘訣

複雑なSoCでのタイミング収束を短期に済ませる秘訣

SoC設計は、ますます高度化し、物理的要因を考慮していないSoCアーキテクチャにより、甚大な被害が生じる事態も散見されるようになっています。そこでこれからのSoC設計で重要になるであろう“秘訣”をご紹介します。 ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

ユニットレベルのクロックゲーティングで消費電力が下がる! モジュール方式のSoCインターコネクト

SoCの低消費電力化で見過ごされがちな“インターコネクト”。ここでは、SoCのダイサイズを縮小し、消費電力を低減できるモジュール方式のSoCインターコネクト技術について紹介する。 32/64bitを追加した高性能MIPS Warrior CPU

32/64bitを追加した高性能MIPS Warrior CPU

イマジネーション・テクノロジーズは、MIPS Warrior CPUのラインアップに、組み込み32ビットMクラスCPU「M6200」「M6250」と64ビットPクラスCPU「P6600」を追加した。 SoCでもマルチコア化は進むのか?

SoCでもマルチコア化は進むのか?

サーバー機器向けのプロセッサは、1つのチップに複数のプロセッサコアを搭載する方向に進化している。この流れはしばらく継続することになりそうだ。では、これと同じ流れが、組み込み機器向けのSoCにも適用されるのだろうか。本稿では、SoCの進化の方向性について考察する。

Copyright © ITmedia, Inc. All Rights Reserved.