半導体(8)―― MOSFETのアバランシェ耐量の使い方(I):中堅技術者に贈る電子部品“徹底”活用講座(67)(2/3 ページ)

チップデザインの対応

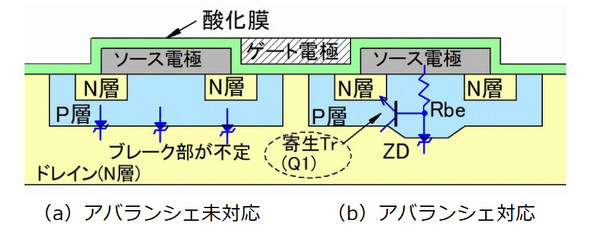

実際の耐量を保証するには単に試験を実施するだけでは保証はできません。図3に該当の断面図を示しますが図3(a)のアバランシェ未対応品ではC-B間のPN接合がブレークする箇所が不定で、どこにブレーク電流が流れるか分かりません。したがってVCB(R)の動作になるのか、狙った箇所以外でブレークして寄生トランジスタがターンオンするかはやってみなければ分かりません。また、チャネル温度が変わってしまうとブレークの様子がどう変化するかかは予測できません。

一方、図3(b)のアバランシェ対応品ではブレークさせたい箇所の耐圧を故意に下げて狙った箇所で必ずブレークするようにチップがデザインされています。

ただし、この説明でも分かるように従来なら例えば550V品として生産できるウエハーを故意に500V程度でブレークさせていることになります。

つまりウエハー自体の耐圧を故意に下げてブレークさせているわけですから必然的にRONの面で不利になります(RON・VdSS2=一定)。

ですがMOSFETの用途の1つである比較的小容量(〜500W程度)のシングルエンド*形スイッチング電源ではどうしてもMOSFETのターンオフ時にトランスコアの励磁電流に比例したスパイク電圧が発生してしまいます。このスパイク電圧は励磁電流に比例するので最大スパイク電圧は最大出力時に発生します。しかし機器の稼働時間の過半数を占める定格出力は一般に最大出力より少ない(80%以下)のでCRスナバー回路を使って定格動作のスパイク電圧をMOSFETの最大定格電圧(Vdss)以下に抑制することは比較的簡単です。

しかしながら定格時にVdssを超えない程度のCRスナバー回路の定数では最大出力時にはVdssを超えてしまいます。また最大出力時にVdssを越えないように定数を設定すると定格時のスナバー回路の損失が増加します。

結局、スナバー回路の損失と高耐圧化によるオン抵抗の増加(550V→500V、つまりRON≒1.2倍)を比較すると一般的にはアバランシェ耐量を保証した方が効率を上げやすくなります。

*シングルエンド形:主として図1の1石式のスイッチング電源の型式を指し、フィード・フォワード形、フライバック形、RCC形、などが含まれます。

一方、ハーフ(あるいはフル)ブリッジ形コンバータはダブルエンド形と呼ばれます。この型式の場合、スパイク電圧は電源電圧でクランプされるのでアバランシェ耐量は使用しなくて済みます。

ただし同じ2石式でもPushーPull型は独自の型式になります。

Copyright © ITmedia, Inc. All Rights Reserved.

図3:チップデザインの差

図3:チップデザインの差