注目が集まるチップレット技術に重要な3つの規格:微細化に代わる技術革新へ

SoC(System on Chip)アーキテクチャの微細化は壁に直面する中で注目が集まるチップレット技術。以下は、現在のチップレットの進化において重要と考えられる3つの規格の概要を紹介する。

SoC(System on Chip)アーキテクチャの微細化は壁に直面している。そのため、「チップレット」として一般に知られるヘテロジニアスシングルパッケージシステムにおけるダイツーダイ相互接続への道が開かれつつある。このようなチップレットに最適化されたインターコネクト技術は大きな支持を得ているものの、まだ初期段階にある。

そのため、チップレット間のインターコネクトの標準規格は、新しいマルチダイ半導体時代にとって極めて重要になっている。以下は、現在のチップレットの進化において重要と考えられる3つの規格の概要だ。これらの標準規格は、オープンなチップレットエコシステムを構築する上で重要な役割を果たすと期待される。

Bunch of Wires(BoW)

「Bunch of Wires(BoW)」インターコネクト技術は、単一パッケージ内の1対のダイ間(D2D)のオープンで相互運用可能な物理インタフェースを定義している。同技術では、SoCの分割に最適化された物理層(PHY)を規定して、チップレットのマルチダイ相互接続の基盤を形成している。

米国のスタートアップ企業であるEliyan Corporationの創業CEO(最高経営責任者)であるRamin Farjadrad氏は、BoWの基礎となる独自のインターコネクト技術を開発し、2018年に高効率ハードウェア技術の実現を目指す共同コミュニティー「Open Compute Project(OCP)」に同技術の標準化を提案した。同技術はその後、チップレットインターコネクトスキームとしてOCPに採用された。

Universal Chiplet Interconnect Express(UCIe)

ダイツーダイ接続のオープンな業界標準規格である「Universal Chiplet Interconnect Express(UCIe)」は、半導体およびパッケージング企業、ファウンドリー、クラウドサービスおよびIP(Intellectual Property)サプライヤーなど、80社を超える企業のコンソーシアムによって2022年3月に発表された。これは、マルチダイシステムの異種統合に向けた重要な一歩であり、同コンソーシアムは、半導体チップレットの新たな設計エコシステムの構築を目指している。

UCIeは、パッケージレベルでのプラグアンドプレイインターコネクトを提供し、さまざまなサプライヤーの異なるプロセス技術が適用されたダイ間の相互運用性を合理化する。BoWインターコネクトと同じシグナリングおよびクロッキングスキームとアーキテクチャの基礎をベースにしていて、現在「UCIe 1.1」仕様を利用可能だ。

高帯域幅メモリ(HBM)

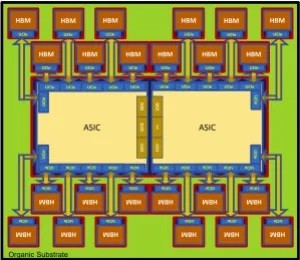

厳密にはチップレットの標準ではないが、より小さなスペースにより多くのメモリチップをパッケージングできることから、チップレット設計に欠かせない要素になりつつある。HBMは、シリコン貫通ビア(TSV)と呼ばれる垂直チャネルを使用することで、さまざまな層のメモリチップを相互に積み重ねることができる。当初は、メモリとプロセッサ間のデータ移動距離を短縮するために設計された。

HBMは当初、データセンターやクラウドコンピューティングにおける計算集約型アプリケーション向けに考案されたが、DRAMチップを垂直に積み重ねることができるため、現在ではチップレット設計に大いに関連した技術となっている。そのため、いくつかの新しいチップレットソリューションでは、HBMプロトコルだけでなくUCIeもサポートしている。

【翻訳:滝本麻貴、編集:EDN Japan】

関連記事

米制裁下のHuaweiが開発、初の中国製5Gチップを分析

米制裁下のHuaweiが開発、初の中国製5Gチップを分析

米国TechInsightは、HuaweiがSMICの7nmプロセスによって、初の中国製5Gスマートフォン向けSoCを開発したと分析している。同社のレポートおよび関連報道が明らかにした詳細や、同社の今後について考察する。 半導体開発向けのAI設計ソリューション、シノプシス

半導体開発向けのAI設計ソリューション、シノプシス

シノプシスは、半導体の設計や検証、テスト、製造向けのAIベース設計ソリューション「Synopsys.ai」を発表した。開発者は、システムアーキテクチャの開発から設計、製造まで全ての半導体開発工程にAIを取り入れられるようになる。 サブ6GHzやミリ波に対応、5Gスマートフォン向けSoC

サブ6GHzやミリ波に対応、5Gスマートフォン向けSoC

メディアテックは、クロック速度や内蔵GPUの性能が向上したハイエンドスマートフォン向けSoC「Dimensity 9200+」を発表した。同製品を搭載したスマートフォンが、2023年5月に発売される予定だ。 TSMC「3nm」世代の現在地

TSMC「3nm」世代の現在地

2022年12月に、3nmプロセスノードでの製造を開始したTSMC。3nmにまつわるTSMCの動向や事業規模についてまとめた。 広帯域幅メモリ内蔵の新プラットフォーム

広帯域幅メモリ内蔵の新プラットフォーム

ザイリンクスは、「Versal ACAP」の新製品「Versal HBM」シリーズを発表した。高速メモリ、データ保護機能、適応型演算機能を統合し、データセンター、有線ネットワーク、テスト、計測、航空宇宙、防衛に適する。 CXLをサポートする、10nmプロセスのFPGA

CXLをサポートする、10nmプロセスのFPGA

インテルは、同社の10nmプロセス技術をベースにしたFPGAファミリー「Agilex」の出荷を開始した。既存のFPGA「Stratix 10」に比べ、性能を最大40%向上、消費電力を最大40%削減できる。

Copyright © ITmedia, Inc. All Rights Reserved.

![BoWはD2DインターコネクトのためのオープンなPHY仕様で、並列インタフェースを提供し、有機基板や先進パッケージング技術で実装できる[クリックで拡大] 出所:Eliyan Corporation](https://image.itmedia.co.jp/edn/articles/2309/12/jn20230912CHIPLET001.jpg)

![UCIeは、パッケージ内のチップレットの主要性能指標を定義している[クリックで拡大] 出所:UCIe](https://image.itmedia.co.jp/edn/articles/2309/12/jn20230912CHIPLET002.jpg)

もともと高性能コンピューティング(HPC)アプリケーション用に設計されたHBMは、チップレットの設計エコシステムにおいて重要な役割を獲得しつつある 出所:Eliyan Corporation

もともと高性能コンピューティング(HPC)アプリケーション用に設計されたHBMは、チップレットの設計エコシステムにおいて重要な役割を獲得しつつある 出所:Eliyan Corporation