半導体(8)―― MOSFETのアバランシェ耐量の使い方(I):中堅技術者に贈る電子部品“徹底”活用講座(67)(1/3 ページ)

今回からはMOSFETの構造に起因するアバランシェ耐量と呼ばれるサージ耐量を使う上での注意点について説明します。この特性を使うには半導体メーカーでの作り込みと正しい検査、そしてユーザーの正しい使い方、の3点が全て満たされることが必要です。この耐量を上手く使いこなすことができれば効率を上げ(損失低減)ながら信頼性を確保できます。

前回まではいわゆるカタログ上の特性項目について使いこなす上での注意点について説明してきました。

今回からはMOSFETの構造に起因するアバランシェ耐量と呼ばれるサージ耐量を使う上での注意点について説明します。

この特性を使うには半導体メーカーでの作り込みと正しい検査、そしてユーザーの正しい使い方、の3点が全て満たされることが必要です。この耐量を上手く使いこなすことができれば効率を上げ(損失低減)ながら信頼性を確保できます。

MOSFETの使い方

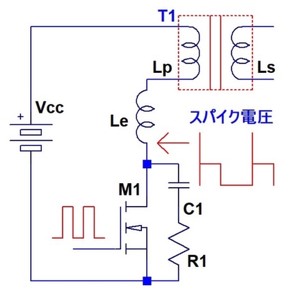

パワーMOSFETの主要な用途であるSW電源の代表的な回路を図1に示します。

電圧変換用トランス(T1)の巻線Lpに加わる電圧をMOSFET(M1)でオン/オフして電圧を2次巻線Lsに伝えますがM1がターンオフするとT1の巻線Lp、Lsの結合の不完全さによって生じる漏れインダクタンスLeによってヒゲ状のスパイク電圧がM1のD-S間に発生します。

M1の電圧ストレスを軽減するために一般には図1のC1、R1によるスナバー回路などでスパイク電圧を低減させますが吸収したエナルギーをR1で熱に変えるためどうしてもSW電源の変換効率が低下してしまいます。

しかし実際にはパワーMOSFETにはアバランシェ耐量と呼ばれるサージ耐量があり、MOSFETのチップデザインが対応できていれば瞬間的にはチャネル温度が許す範囲で定格電圧を超えて使うことができ、CRスナバーの損失を低減できます。ここではこの能力について説明します。

アバランシェ機構

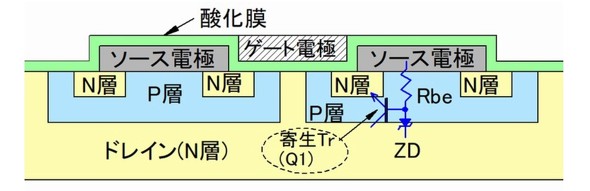

パワーMOSFETは今まで説明してきたように図2に示すようなセルと呼ばれる基本構造を数万〜数百万個並列に接続した構造を採っています。この断面図からドレインのN層と遮断層のP層、ソ−スのN層との間で寄生のNPNトランジスタ(Q1)を構成しているのが分かります。

このQ1のコレクタ(C)−ベース(B)間に該当する接合部に一定の電圧(アバランシェ電圧=VAV)を超える電圧が印加されると図2中のダイオードZDがブレークダウンします。

しかし、このQ1のベース(B)、エミッタ(E)に該当する接合部はソース電極で短絡されておりB-E間の短絡抵抗はP層中の低い拡散抵抗Rbeが主体になります。したがってこのZDのブレークダウン電流がソース電極に向かって流れてもRbeの両端電圧が0.7V(Vbe)に達しなければ寄生トランジスタであるQ1はオンしません。もちろん図2の基本セルは極微で1セル当たり数十μA単位でしかブレークダウン電流を流すことができませんが100万セルもそろえばチップ全体としてA単位のブレークダウン電流を流すことが可能になります。しかもこの動作は一般のトランジスタのVCB(R)を測定していることと等価ですのでQ1にダメージは残りません。

したがって温度が許される範囲でブレークダウンを繰り返すこと、つまりサージ電圧を連続して吸収することが可能になります。この耐量がアバランシェ耐量と呼ばれる能力です。以下、このブレークダウン電流を一般的な呼称であるアバランシェ電流と称します。

この耐量を保証するには単に試験で不良品を取り除くだけではダメージセルの内包などから信頼性を保証することはできません。チップに試験のダメージを残さないためにはチップ内の全セルが同じタイミングで同じ動作をするようにチップデザインなどに工夫をする必要があります。

このような背景から拡散工程のバラツキはこの試験の不良率と直結しますのでアバランシェ耐量の不良率は拡散工程の不均一性のパラメーターとして使用可能です。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:SW電源の代表的な回路

図1:SW電源の代表的な回路 図2:MOSFETの基本セル構造

図2:MOSFETの基本セル構造